#### DESAIN HIGH FREQUENCY PWM MENGGUNAKAN CPLD DAN PEMANFAATAN SISTEM SEBAGAI KONTROL PADA DC-DC FLYBACK UP CONVERTER

#### **SKRIPSI**

Sebagai salah satu syarat untuk memperoleh gelar Sarjana Sains dalam bidang Fisika

> oleh : SIGIT KURNIAWAN 0810930056-93

JURUSAN FISIKA

FAKULTAS MATEMATIKA DAN ILMU PENGETAHUAN ALAM

UNIVERSITAS BRAWIJAYA

MALANG

2014

#### LEMBAR PENGESAHAN SKRIPSI

#### DESAIN HIGH FREQUENCY PWM MENGGUNAKAN CPLD DAN PEMANFAATAN SISTEM SEBAGAI KONTROL PADA DC-DC FLYBACK UP CONVERTER

#### oleh : SIGIT KURNIAWAN 0810930056-93

**Pembimbing I**

Pembimbing II

Dr.Ing. Setyawan P Sakti, M.Eng NIP. 19650825 199002 1 001 Hari A Dharmawan, M.Eng., Ph.D NIP. 19690920 199410 01

Mengetahui, Ketua Jurusan Fisika Fakultas MIPA Universitas Brawijaya

> Adi Susilo, Ph.D NIP. 19631227 199103 1 002

#### LEMBAR PERNYATAAN

#### Saya yang bertanda tangan di bawah ini:

Nama : Sigit Kurniawan NIM : 0810930056

Jurusan : Fisika

Penulis Skripsi berjudul

#### DESAIN HIGH FREQUENCY PWM MENGGUNAKAN CPLD DAN PEMANFAATAN SISTEM SEBAGAI KONTROL PADA DC-DC FLYBACK UP CONVERTER

#### Dengan ini menyatakan bahwa:

- 1. Isi dari skripsi yang saya buat adalah benar-benar karya sendiri dan tidak menjiplak karya orang lain, selain nama-nama termaktub di isi dan tertulis di daftar pustaka dalam Skripsi ini.

- 2. Apabila dikemudian hari ternyata skripsi saya tulis terbukti hasil jiplakan, maka saya akan bersedia menanggung segala resiko yang akan saya terima.

Demikian pernyataan ini dibuat dengan segala kesadaran.

| Malang,     |  |

|-------------|--|

| Yang menyat |  |

Sigit Kurniawan NIM. 0810930056

#### DESAIN HIGH FREQUENCY PWM MENGGUNAKAN CPLD DAN PEMANFAATAN SISTEM SEBAGAI KONTROL PADA DC-DC FLYBACK UP CONVERTER

#### **ABSTRAK**

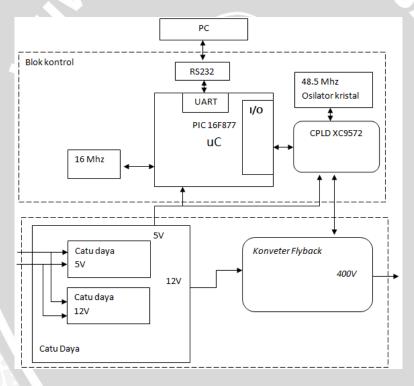

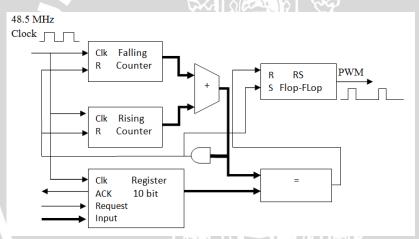

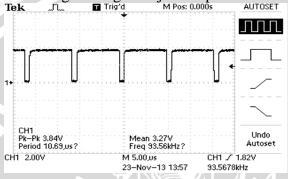

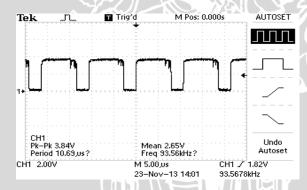

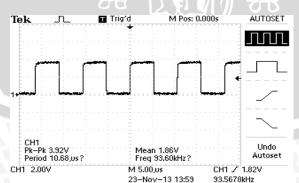

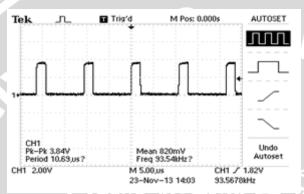

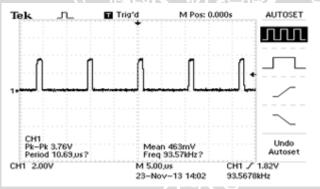

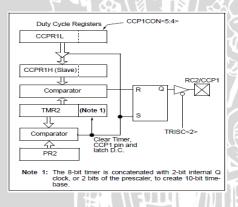

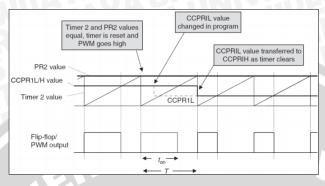

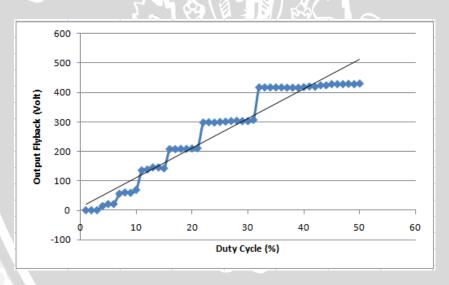

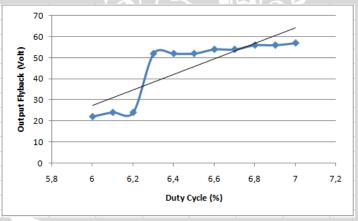

Pulse Width Modulation (PWM) menjadi bagian yang tak terpisahkan dari kebanyakan sistem kontrol. Salah satu kegunaan dari PWM adalah sebagai pengontrol daya pada rangkaian konverter DC-DC/DC-AC. Penggunaan PWM dengan frekuensi tinggi selalu menjadi alternatif untuk mengurangi besarnya ukuran transfomator pada konverter *flyback*. Frekuensi tinggi PWM dapat dihasilkan jika mengunakan model pencacah dengan kemampuan menghitung cepat. Teknik pencacahan rising dan falling untuk model pencacah yang dirancang mampu menghasilkan PWM dengan frekuensi lebih tinggi daripada teknik PWM yang dibangun pada mikrokontroller PIC16F87X. Besarnya frekuensi PWM yang dibangun pada komponen CPLD bergantung pada resolusi dan osilator kristal yang digunakan, nilai frekuensi yang mampu dihasilkan untuk resolusi PWM 10 bit dan frekuensi osilator kristal 48 MHz pada arsitektur PWM yang telah dirancang adalah 93.5 kHz. Desain high frequency PWM pada komponen CPLD dapat digunakan sebagai kontrol pada konverter Flyback untuk menaikkan tegangan DC dari 12V ke 400V.

**Kata kunci:** *Pulse Width Modulation*, Konverter *Flyback*, CPLD, Teknik pencacahan *Rising* dan *Falling*

# DESIGN OF HIGH FREQUENCY PWM USING CPLD AND IMPLEMENTATION SYSTEM FOR DC-DC FLYBACK UP CONVERTER CONTROL

#### **ABSTRACT**

Pulse Width Modulation (PWM) becomes the important part for most control systems. One of many functions of PWM is as power control for DC-DC/DC-AC converter circuit. The use of high frequency PWM always be alternative for decreasing size of transfomer in Flyback converter. High frequency PWM can be produced by using counter model with fast counting capability. The rising and falling counter that has been designed can produce PWM frequency that is higher than frequency that has been developed with PWM technique using microcontroller PIC16F87X. The result of PWM frequency using CPLD depends on resolution of N-bit counter and frequency of crystal oscilator that used. Frequency value that can be produced for 10 bit resolution of counter and 48 MHz frequency of crystal oscilator in PWM architecture which has been designed is 93.5 kHz. High frequency PWM using CPLD can be used as control on Flyback converter for step up DC voltage from 12V to 400V.

**Keyword:** Pulse Width Modulation, Flyback converter, CPLD, The Rising and Falling counting technique

#### KATA PENGANTAR

Alhamdulillahirabbil alamin, dengan ungkapan rasa syukur pada Allah, sehingga penulis dapat menyelesaikan penyusunan skripsi yang merupakan salah satu syarat untuk memperoleh gelar sarjana sains dalam bidang fisika. Pada kesempatan ini penulis menghaturkan terimakasih kepada:

- a. Kedua orang tua, serta keluarga yang selalu memberi dukungan kepada penulis.

- b. Dr.Ing. Setyawan P Sakti, M.Eng. dan Hari A Dharmawan, M.Eng.,Ph.D. selaku pembimbing skripsi atas segala bimbingan selama skripsi.

- c. Dr. Sunaryo, M.Si. selaku dosen pembimbing akademik, atas semua nasihat dan bimbingan Bapak selama ini

- d. Sdr. Hari Murti Widodo. serta rekan-rekan di Laboratorium Instrumentasi dan Pengukuran Jurusan Fisika.

- e. Kepada teman-teman Fisika angkatan 2008.

- f. Seluruh *civitas academica* Jurusan Fisika atas bantuan dan kerjasamanya.

Semoga Allah membalas kebaikan dan pertolongan yang telah diberikan.

Penulisan skripsi ini adalah upaya optimal dari penulis, namun masih banyak kekurangan yang harus diperbaiki. Oleh karenanya, penulis mengharapkan kritik dan saran yang membangun dari pembaca. Semoga skripsi ini bermanfaat, terutama bagi mahasiswa Fisika, dan masyarakat pada umumnya.

Malang, Desember 2013

Penulis

# DAFTAR ISI

|                                                  | Halaman                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HALAMAN JUDUL                                    | i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HALAMAN PENGESAHAN                               | ii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| HALAMAN PERNYATAAN                               | iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ABSTRAK / ABSTRACT                               | iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| KATA PENGANTAR                                   | vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DAFTAR ISI                                       | vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DAFTAR GAMBAR                                    | <u>i</u> x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DAFTAR TABEL                                     | xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DAFTAR GRAFIK                                    | xii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DAFTAR LAMPIRAN                                  | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BAB I PENDAHULUAN                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.1 Latar Belakang                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.2 Rumusan Masalah                              | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.3 Batasan Masalah                              | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.4 Tujuan Penelitian 1.5 Manfaat Penelitian     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.5 Manfaat Penelitian                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                  | $egin{array}{c} egin{array}{c} \egin{array}{c} egin{array}{c} \egin{array}{c} \egin{array}$ |

| BAB II TINJAUAN PUSTAKA 2.1                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| nik PWM                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.1.1 Teknik analog                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.1.1.1 Multiple Pulse Width Modulation          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.1.1.2 Sinusoidal Pulse Width Modulation        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.1.2 Teknik digital<br>2.2                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

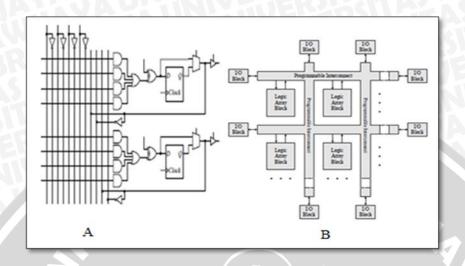

| grammable Logic Device (PLDs)                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A 111 97 A 3 A 3 A 4 A 4 A 4 A 4 A 4 A 4 A 4 A 4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.2.1 Complex Programmable Logic Device (        | CPLD) 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

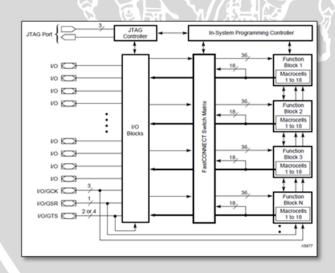

| 2.2.1 Xilinx XC9500 Family                       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.3                                              | Mik                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| rokontroller                                     | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

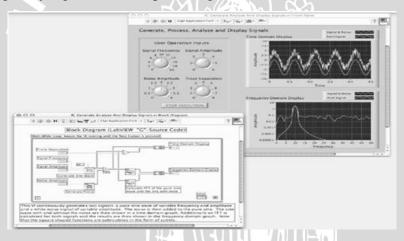

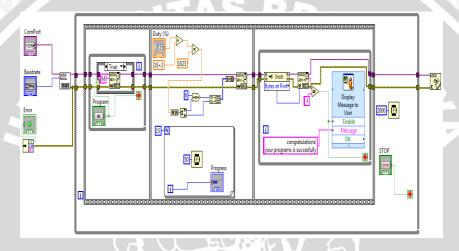

| 2.4                                              | Lab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VIEW                                             | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

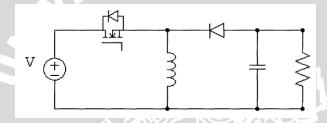

| 2.5                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

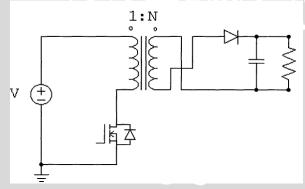

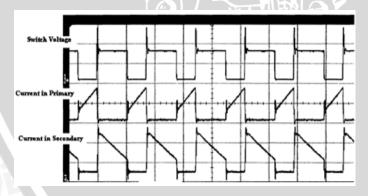

| auan Konsep Konverter Flyback                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

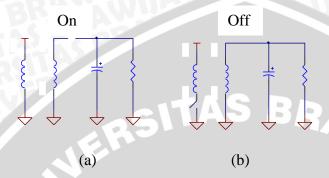

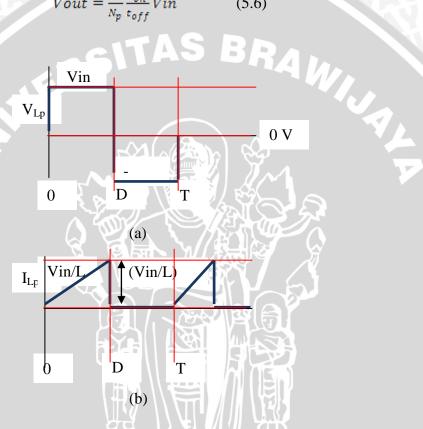

| 2.5.1 Continous Conduction Mode (CCM)          | 16       |

|------------------------------------------------|----------|

| BAB III METODE PENELITIAN                      |          |

| 3.1 Waktu dan Tempat Penelitian                | 19       |

| 3.2 Tahapan Pengerjaan                         |          |

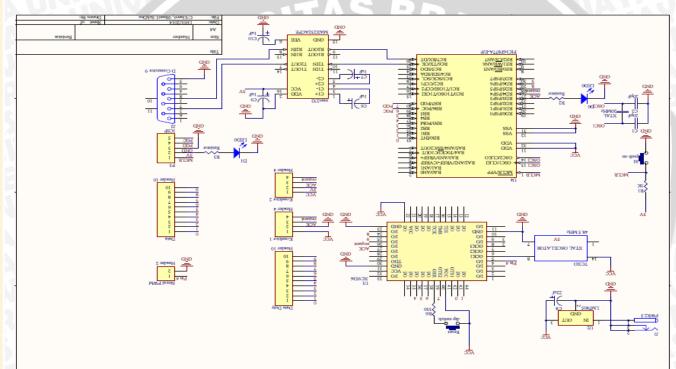

| 3.3                                            |          |

| cangan Sistem                                  |          |

| 3.3.1                                          |          |

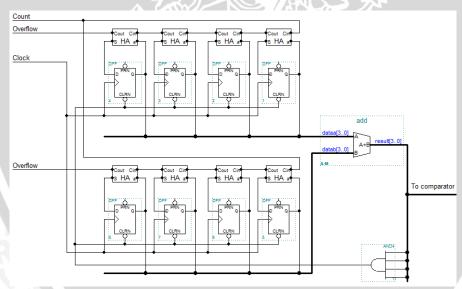

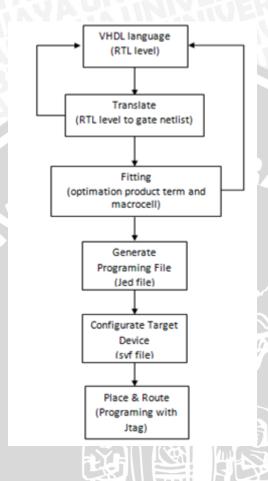

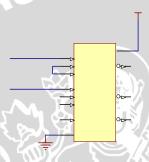

| erancangan teknik digital PWM pada k CPLD      |          |

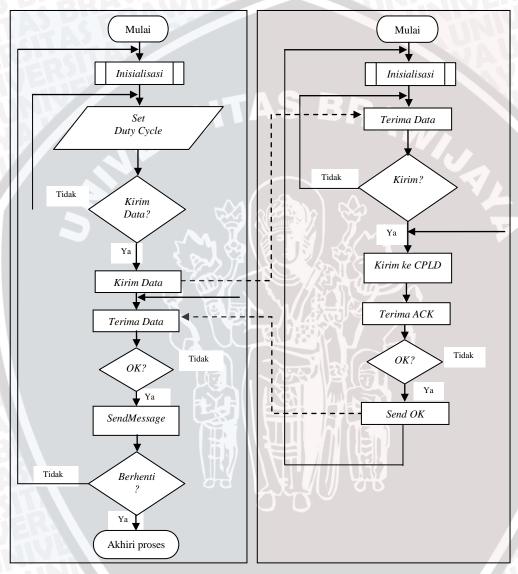

| 3.3.2                                          |          |

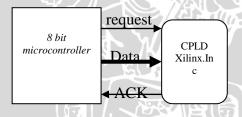

| erancangan sistem pengiriman data              |          |

| menentukan duty cycle PWM                      |          |

| 3.3.3                                          |          |

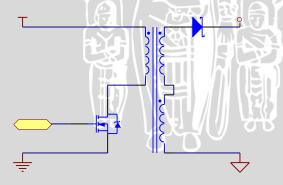

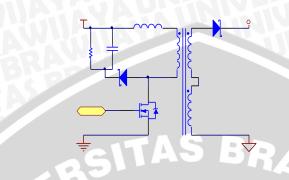

| erancangan sistem elektronik untuk             |          |

| Flyback                                        | 25       |

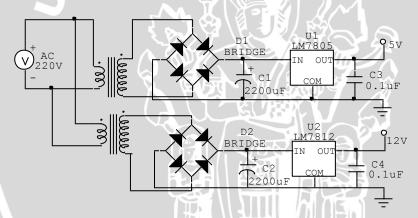

| 3.3.4                                          |          |

| atu Daya                                       | 27       |

| 3.4 Pembuatan Alat                             |          |

| 3.4.1 Implementasi desain ke dalam CPLD        |          |

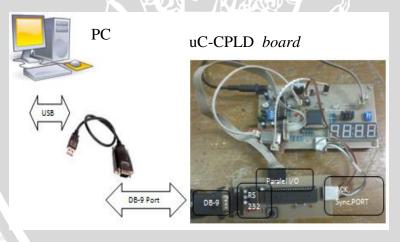

| 3.4.2 Pembuatan sistem komunikasi data dari PC |          |

| melalui mikrokontroller                        | 29       |

| 3.4.3 Pembuatan konverter Flyback              | 31       |

|                                                |          |

| BAB IV HASIL DAN PEMBAHASAN                    |          |

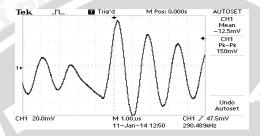

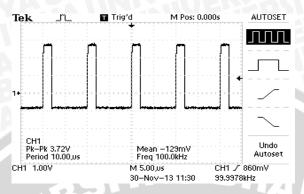

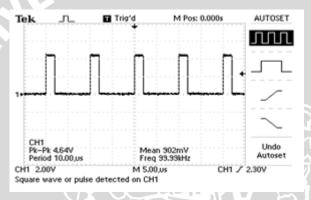

| 4.1                                            |          |

| Pengujian CPLD sebagai pembangkit PWM          |          |

| 4.1.1                                          |          |

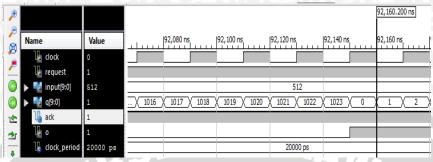

| asil sintesis untuk teknik digital PWM yang    |          |

| pada komponen CPLD                             |          |

| Perbandingan nilai frekuensi PWM yang d        |          |

| antara CPLD dengan mikrokontroller             |          |

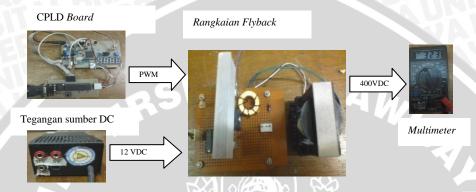

| 4.3                                            | 31       |

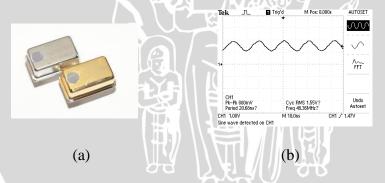

| Pembuatan dan pengujian rangkaian penguat      | tegangan |

| keluaran PWM                                   |          |

|                                                |          |

| 4.4                                     |        |

|-----------------------------------------|--------|

| Pengujian CPLD sebagai kontrol rangkaia |        |

| konverter DC-DC                         | 41     |

|                                         |        |

| BAB V PENUTUP                           |        |

| 5.1                                     | K      |

| esimpulan                               | 44     |

| 5.2                                     | S      |

| aran                                    | 44     |

| / 23                                    | 4 1/10 |

| DAFTAR PUSTAKA                          | 46     |

|                                         |        |

# DAFTAR GAMBAR

| Halama                                                                                            |

|---------------------------------------------------------------------------------------------------|

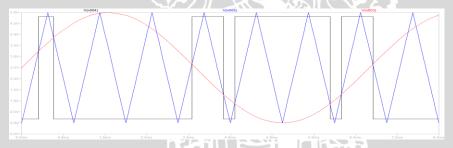

| Gambar 2.1 Hasil simulasi dari LTSpice untuk metode <i>Multiple PWM</i>                           |

| Gambar 2.2. Hasil simulasi dari LTSpice metode <i>Sinusoidal PWM</i>                              |

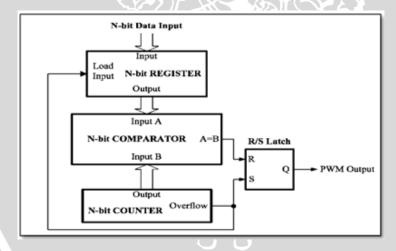

| Gambar 2.3. Blok diagram dari teknik digital PWM7                                                 |

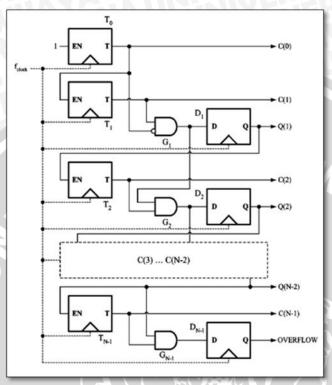

| Gambar 2.4. Blok diagram dari Pencacah 8                                                          |

| Gambar 2.5. a) LAB dengan dua macrocells 10                                                       |

| b) Rangkaian internal dari CPLD yang terdiri dari LAB,                                            |