# BAB V PENGUJIAN DAN ANALISIS

Bab ini berisi penjelasan prosedsur pengujian dari alat yang telah dirancang untuk mengetahui sistem dapat bekerja dengan baik sesuai dengan perencanaan. pengujian dilakukan dengan memberikan perubahan pada *input* blok diagram dan mengamati *output* blok diagram yang diuji. Data hasil pengujian yang diperoleh nantinya akan dianalisis untuk dijadikan acuan dalam mengambil kesimpulan.

Pengujian dilakukan pada tiap-tiap blok sistem. Adapun blok-blok yang diuji adalah:

- Pengujian modul rangkaian RFID

- Pengujian Mikrokontroler

- Pengujian rangkaian driver

- pengujian sistem secara keseluruhan

### 5.1 Pengujian Modul Rangkaian RFID

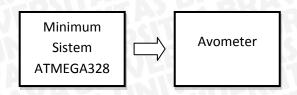

Pengujian RFID bertujuan untuk mengetahui keberhasilan dari pembaca RFID untuk membaca data yang terdapat pada kartu RFID. Blok pengujian RFID ditunjukan dalam gambar 5.1.

Gambar 5.1. Diagram blok pengujian RFID

Hasil pengujian data keluaran ditunjukan dalam gambar 5.2.

Gambar 5.2. Hasil pengujian rangkaian RFID dan LCD dengan tiga tag RFID

Dari hasil pengujian dalam gambar 5.2 dapat dilihat bahwa masukan yang diberikan oleh RFID reader yang berupa nomor dari tag RFID dapat ditampilkan pada LCD.

## 5.1.1. Hasil Pengujian

Tabel 5.1. Pengujian Modul RFID

| No. | Kode Tag       | Nama tag |

|-----|----------------|----------|

| 1   | D5-86-A4-E5-12 | Tag 1    |

| 2   | F0-63-18-35-BE | Tag 2    |

| 3   | 70-23-18-35-7E | Tag 3    |

Tabel 5.2. Prosentase keberhasilan pembacaan kartu tanpa penghalang

| Jarak | Pengujian 10 x |       |       |  |  |  |  |

|-------|----------------|-------|-------|--|--|--|--|

| (cm)  | Tag 1          | Tag 2 | Tag 3 |  |  |  |  |

| 0.5   | 100 %          | 100 % | 100 % |  |  |  |  |

| 1     | 100 %          | 100 % | 100 % |  |  |  |  |

| 1.5   | 100 %          | 100 % | 100 % |  |  |  |  |

| 1.6   | 100 %          | 100 % | 100 % |  |  |  |  |

| 1.7   | 100 %          | 100 % | 100 % |  |  |  |  |

| 100 %       | 100 % | 100 % | 1.8 |

|-------------|-------|-------|-----|

| 50 %        | 60 %  | 30 %  | 1.9 |

| 0 %         | 0 %   | 0%    | 2.0 |

| \<br>\<br>\ | 0 %   | 0%    | 2.0 |

Tabel 5.3. Prosentase keberhasilan pembacaan kartu dengan penghalang plastik

| Jarak | Pengujian 10x |       |       |  |  |  |  |  |

|-------|---------------|-------|-------|--|--|--|--|--|

| (cm)  | Tag 1         | Tag 2 | Tag 3 |  |  |  |  |  |

| 0.5   | 100 %         | 100 % | 100 % |  |  |  |  |  |

| .45   | 100 %         | 100 % | 100 % |  |  |  |  |  |

| 1.5   | 100 %         | 100 % | 100 % |  |  |  |  |  |

| 1.6   | 100 %         | 100 % | 100 % |  |  |  |  |  |

| 1.7   | 100 %         | 100 % | 100 % |  |  |  |  |  |

| 1.8   | 20 %          | 10 %  | 10 %  |  |  |  |  |  |

| 1.9   | 0 %           | 0 %   | 0 %   |  |  |  |  |  |

| 2     | 0.%           | 0 %   | 0 %   |  |  |  |  |  |

Tabel 5.4. Prosentase keberhasilan pembacaan kartu dengan penghalang logam

| Jarak | Pengujian 10x |       |       |  |  |  |  |  |

|-------|---------------|-------|-------|--|--|--|--|--|

| (cm)  | Tag 1         | Tag 2 | Tag 3 |  |  |  |  |  |

| 0     | 100 %         | 100 % | 100 % |  |  |  |  |  |

| 0.1   | 0 %           | 0 %   | 0 %   |  |  |  |  |  |

| 0.2   | 0 %           | 0 %   | 0 %   |  |  |  |  |  |

| 0.3   | 0 %           | 0 %   | 0 %   |  |  |  |  |  |

| 0.4   | 0 %           | 0 %   | 0 %   |  |  |  |  |  |

| 0.5   | 0 %           | 0 %   | 0 %   |  |  |  |  |  |

#### 5.1.2. Analisis Data

Dari hasil pengujian tabel 5.1, dapat diamati kode tag yang terdeteksi oleh RFID reader merupakan identitas tag yang terdeteksi.

Pengujian berikutnya dilakukan menjadi dua bagian, yaitu pengujian tanpa penghalang dan dengan penghalang. Tabel 5.2 dapat disimpulkan bahwa dengan pengujian tanpa penghalang, pembacaan tag agar bekerja secara baik dapat dilakukan dengan jarak maksimal ≤ 1.8 cm.

Tabel 5.3 menujukan jarak maksimal pembacaan tag agar bekerja baik jika terdapat penghalang plastik dapat dilakukan adalah ≤ 1,7 cm. Dari hasil pengujian tabel 5.4 menunjukan bahwa pengujian dilakukan dengan penghalang logam, dapat diamati bahwa tag terdeteksi oleh RFID reader dengan jarak 0 cm.

Dengan jarak lebih jauh, tag pasif tidak mampu terbaca oleh RFID reader. RFID reader dapat mendeteksi kartu tag meskipun terhalang benda lain. Pada penghalang logam secara signifikan mengurangi fluksi dari medan magnet. Akibatnya RFID tidak dapat bekerja dengan baik.

## 5.2. Pengujian Rangkaian Minimum Sistem ATMega 328P

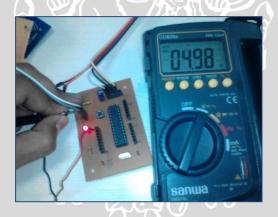

Dalam pengujian minimum sistem alat dan komponen yang digunakan antara lain rangkaian minimum sistem ATMega 328P dan Avometer digital. Dalam pengujian minimum sistem ini terdapat dua pengujian yaitu:

### Pengujian I/O

Pengujian I/O dilakukan dengan cara memberi logika low (0) dan high (1) pada masing-masing port pada rangkaian minimum sistem. Lalu mencatat tegangan yang dihasilkan masing-masing port sesuai dengan logika yang diberikan. Diagram blok pengujian I/O minimum sistem ditunjukkan dalam Gambar 5.6, Tabel 5.5 menunjukkan tegangan output minimum sistem ATMega 328P logika 1 dan Tabel 5.6 menunjukkan tegangan output minimum sistem ATMega 328P logika 0.

Gambar 5.3. Diagram Blok pengujian I/O minimum sistem

Tabel 5.5. Tegangan *Output* Minimum Sistem ATMEGA 328P logika 1

| H                        | 300    |      |      |      | P       | ORT B  |         |        |      |      |      |         |

|--------------------------|--------|------|------|------|---------|--------|---------|--------|------|------|------|---------|

| PORT Logika Percobaan(V) |        |      |      |      |         |        |         | Rata – |      |      |      |         |

| TOKT                     | Input  | 1    | 2    | 3    | 4       | 5      | 6       | 7      | 8    | 9    | 10   | rata(V) |

| B.0                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| B.1                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| B.2                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| B.3                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| B.4                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| B.5                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

|                          |        |      |      | 100  | Rata –r | ata    | P/      |        |      |      |      | 4.98    |

|                          |        |      |      | 1    | P       | ORT C  |         |        |      |      |      |         |

| PORT                     | Logika |      | Ų    |      | 4       | Percol | oaan(V) |        |      |      |      | Rata –  |

| FORT                     | Input  | 1    | 2    | 3    | 4       | 5      | 6       | 7      | 8 /  | 9    | 10   | rata(V) |

| C.0                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| C.1                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| C.2                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| C.3                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| C.4                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| C.5                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| C.6                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| C.7                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| 0511                     | 41     |      |      | ]    | Rata –r | ata    |         |        |      |      |      | 4.98    |

| 11111                    |        |      |      |      | P       | ORT D  |         |        |      |      |      |         |

| PORT                     | Logika |      |      |      |         | Percol | aan(V)  | )      |      |      |      | Rata –  |

| TORT                     | Input  | 1    | 2    | 3    | 4       | 5      | 6       | 7      | 8    | 9    | 10   | rata(V) |

| D.0                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| D.1                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| D.2                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| D.3                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| D.4                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| D.5                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| D.6                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| D.7                      | 1      | 4.98 | 4.98 | 4.98 | 4.98    | 4.98   | 4.98    | 4.98   | 4.98 | 4.98 | 4.98 | 4.98    |

| Rata –rata 4.98 |

|-----------------|

|-----------------|

<sup>\*</sup> Tegangan Output Minimum Sistem ATMEGA328P logika 1berdasarkan teori adalah 5 V

Tabel 5.6. Tegangan *Output* Minimum Sistem ATMEGA 328P logika 0

|             | MALA   |    |     | H  | PO         | ORT B       |               |             | 417  |    | 45 | TAN     |

|-------------|--------|----|-----|----|------------|-------------|---------------|-------------|------|----|----|---------|

| PORT        | Logika | HA |     | 14 |            | Percob      | aan(V)        |             | Mari |    |    | Rata –  |

| TORT        | Input  | 1  | 2   | 3  | 4          | 5           | 6             | 7           | 8    | 9  | 10 | rata(V) |

| B.0         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| B.1         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| B.2         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| B.3         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| B.4         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| B.5         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0/   | 0  | 0  | 0       |

| B.6         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| B.7         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| <b>V</b> // |        |    |     | Ra | ata –ra    | ta          | $\overline{}$ |             |      |    | Y  | 0       |

|             |        |    |     | 7  | √ PO       | ORT C       |               | 5           |      |    |    |         |

| DODT        | Logika |    |     | A  | 91         | Percob      | aan(V)        |             | 1    |    |    | Rata –  |

| PORT        | Input  | 1  | 2   | 3  | (4)        | 5           | 6             | ×7          | 8_   | 9  | 10 | rata(V) |

| C.0         | 0      | 0  | 0   | -0 | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| C.1         | 0      | 0  | 0   | 0  | 0          | 0           | 70            | 0           | 0    | 0  | 0  | 0       |

| C.2         | 0      | 0  | 0   | 00 | 0          | 07          | 0             | 0           | 0 😭  | 0  | 0  | 0       |

| C.3         | 0      | 0  | 0   | 0  | 0          | <b>(0</b> ) | 0             | 0           | 0    | 0  | 0  | 0       |

| C.4         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| C.5         | 0      | 0  | 0   | 06 | 0          | 05          | 0             | <b>3</b> 0= | 0    | 0  | 0  | 0       |

| C.6         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| C.7         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

|             |        |    |     | Ra | ata –ra    | ta          | 1             |             |      |    |    | 0       |

|             |        |    |     | 11 | PO         | ORT D       |               | i I (F      |      |    |    |         |

| рорт        | Logika |    |     | Щ  | <b>Y</b> 1 | Percob      | aan(V)        | با          |      |    |    | Rata –  |

| PORT        | Input  | 1  | 2   | 3  | 4          | 5           | 6             | 7           | 8    | 9  | 10 | rata(V) |

| D.0         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| D.1         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| D.2         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| D.3         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| D.4         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| D.5         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| D.6         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

| D.7         | 0      | 0  | 0   | 0  | 0          | 0           | 0             | 0           | 0    | 0  | 0  | 0       |

|             | 5 DIEN | NH | WIN |    | ita –ra    |             |               | IIR         |      | TW | EN | 0       |

<sup>\*</sup> Tegangan Output Minimum Sistem ATMEGA328P logika 0 berdasarkan teori adalah 0 V

Dari hasil diatas dapat dihitung % kesalahan (error) dapat dirumuskan dengan menggunakan persamaan (5-1):

% kesalahan =

$$\frac{|data\ praktek-data\ teori|}{data\ teori} \times 100\%...(5-1)$$

Hasil penghitungan % error dari pengambilan data pada port I/O minimum sistem mikrokontroler ATMega 328P ditunjukkan dalam Tabel 5.7. dan untuk Gambar 5.4 menunjukkan pengujian I/O.

Tabel 5.7. Hasil penghitungan % error I/O

| PORT     | Logika          | % error | Logika | % error |

|----------|-----------------|---------|--------|---------|

| PORT B   | -1/1            | 0.40%   | C(0)   | 0%      |

| PORT C   | 1               | 0.40%   | 0      | 0%      |

| PORT D   | 120             | 0.40%   | 5.0    | 0%      |

| Rata –ra | ta <i>error</i> | 0.40%   |        | 0 %     |

Gambar 5.4. Pengujian I/O

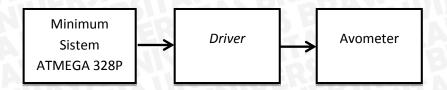

### 5.3. Pengujian Rangkaian Driver

Pengujian driver dilakukan dengan cara mengambil data arus yang dihasilkan oleh Arus forward ketika logika diberi high dan diberi low. Diagram blok dari pengujian driver ditunjukkan dalam Gambar 5.5 dan Gambar 5.6 menunjukkan pengujian dari driver.

Gambar 5.5. Blok Diagram Pengujian Driver

Gambar 5.6. Pengujian Rangkaian Driver

Alat yang digunakan dalam pengujian *driver* adalah rangkaian minimum sistem, avometer dan rangkaian *driver*. Setelah data didapat maka dibandingkan dengan hasil secara teori. Untuk penghitungan secara teori besar arus  $I_F$  dengan  $I_{cmin}$  = 34,09 mA, CTR = 100% adalah:

$$CTR = \frac{Ic}{IF} x 100\%$$

$$IF = \frac{Ic}{CTR} x 100\%$$

$$IF = \frac{34,09}{100\%} x 100\%$$

$IFmin = 34,09 \, mA$

Untuk hasil pengujian dari perancangan *driver* transistor ini ditunjukkan dalam Tabel 5.8.

| Tegangan |       | Perc | Rata- | Teori |       |          |                     |

|----------|-------|------|-------|-------|-------|----------|---------------------|

| Input    | 1     | 2    | 3     | 4     | 5     | rata(mA) | I <sub>F</sub> (mA) |

| 5        | 32,20 | 33,7 | 33,7  | 33,0  | 32,90 | 33.10    | 34.09               |

| 0        | 0     | 0    | 0     | 0     | 0     | 0        | 0                   |

Tabel 5.8. Hasil Pengujian Driver

Dari Hasil pengujian, Saat diberi logika 1 driver aktif tapi arus yang dihasilkan sangat kecil. Dari data yang didapat dari pengujian juga dapat dihitung % kesalahan yaitu dengan membandingkan hasil yang didapat dalam pengujian dan hasil yang didapat pada perhitungan secara teori. Di bawah ini merupakan % kesalahan dari perancangan:

% kesalahan =

$$\frac{|data \ pengujian - data \ teori|}{data \ teori|} \ x \ 100\%$$

$$= \frac{|33,10 - 34,09|}{34,09} \ x \ 100\%$$

$$= 2,90 \%$$

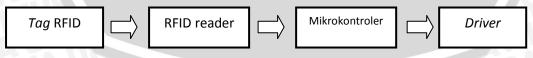

## 5.4. Pengujian Keseluruhan Sistem

Pengujian keseluruhan sistem ini bertujuan untuk menguji sistem dapat berjalan dengan baik. Pengujian ini dilakukan dengan cara menggabungkan semua perangkat/interface yang telah dirancang dari perancangan semua hardware dan perancangan software. Untuk diagram blok dari pengujian keseluruhan sistem ditunjukkan pada Gambar 5.7.

Gambar 5.7. Blok pengujian keseluruhan sistem

Setelah semua perangkat telah tepasang selanjutnya mengambil data berupa arus I<sub>E</sub>, output tegangan pada pin 14, dan output tegangan pada pin 15 berdasarkan perubahan input tag RFID. Untuk pengujian keseluruhan sistem ditunjukkan dalam Gambar 5.8 dan Tabel 5.9 menunjukkan data dari pengujian keseluruhan sistem.

Gambar 5.8. Pengujian Keseluruhan Sistem

|           | Tabel 5.9. Hasil pengu | ijian keseluruh | an sistem           |             |

|-----------|------------------------|-----------------|---------------------|-------------|

| pengujian | Tag                    | Vpin15(V)       | I <sub>F</sub> (mA) | Driver      |

| 1         | terdaftar              | 4.94            | 32,20               | Aktif       |

|           | Tidak terdaftar        | -0              | 0                   | Tidak aktif |

|           | Tidak ada(wait ±10s)   | 0               | <b>√</b> 0          | Tidak aktif |

| 2         | Terdaftar              | 4.93            | 33,70               | Aktif       |

|           | Tidak terdaftar        | <b>5.</b> 0     | 0.0                 | Tidak aktif |

|           | Tidak ada(wait ±10s)   | > 0/6           | 0                   | Tidak aktif |

| 3         | Terdaftar              | 4.93            | 32,20               | Aktif       |

|           | Tidak terdaftar        | 0               | 10                  | Tidak aktif |

|           | Tidak ada(wait ±10s)   | 7//05=          | 0                   | Tidak aktif |

| 4         | Terdaftar              | 4.96            | 33,50               | Aktif       |

|           | Tidak terdaftar        | 0               | 0                   | Tidak aktif |

|           | Tidak ada(wait ±10s)   | 0               | 0                   | Tidak aktif |

| 5         | Terdaftar              | 4.94            | 33,70               | Aktif       |

|           | Tidak terdaftar        | 40 0 W          | 0                   | Tidak aktif |

|           | Tidak ada(wait ±10s)   | 0               | 0                   | Tidak aktif |

| 6         | terdaftar              | 4.94            | 32,10               | Aktif       |

|           | Tidak terdaftar        | 0               | 0                   | Tidak aktif |

|           | Tidak ada(wait ±10s)   | _ 0             | 00                  | Tidak aktif |

| 7         | Terdaftar              | 4.93            | 33,70               | Aktif       |

|           | Tidak terdaftar        | 0               | 0                   | Tidak aktif |

|           | Tidak ada(wait ±10s)   | 0               | 0                   | Tidak aktif |

| 8         | Terdaftar              | 4.92            | 32,20               | Aktif       |

|           | Tidak terdaftar        | 0               | 0                   | Tidak aktif |

|           | Tidak ada(wait ±10s)   | 0               | 0                   | Tidak aktif |

| 9         | Terdaftar              | 4.96            | 33,50               | Aktif       |

|           | Tidak terdaftar        | 0               | 0                   | Tidak aktif |

| HILANY    | Tidak ada(wait ±10s)   | 0               | 0                   | Tidak aktif |

| 10        | Terdaftar              | 4.91            | 33,70               | Aktif       |

| S VAL     | Tidak terdaftar        | 0               | 0                   | Tidak aktif |

| TORA      | Tidak ada(wait ±10s)   | 0               | 0                   | Tidak aktif |

Dari pengujian keseluruhan bahwa alat berjalan dengan baik berdasarkan algoritma yang digunakan pada *flowchart* yang dibuat. Dari percobaan didapatkan ketika *tag* yang digunakan sudah terdaftar pada sistem, Vpin 15 rata-rata berilai 4,94, arus *forward* (I<sub>F</sub>) rata-rata bernilai 33,05 mA dan *driver* aktif. Saat *tag* yang digunakan tidak terdaftar terdaftar pada sistem, Vpin 15 berilai 0, arus *forward* (I<sub>F</sub>) bernilai 0 mA dan *driver* tidak aktif. Pada saat pengujian tanpa menggunakan *tag* Vpin 15 berilai 0 V, arus *forward* (I<sub>F</sub>) bernilai 0 mA dan *driver* tidak aktif. Pengujian keseluruhan sistem ini dilakukan dengan kondisi penghalang jika alat ini di implementasikan lebih lanjut.