# IMPLEMENTASI MIKROPROSESOR 8085 DAN SISTEM MEMORI DALAM FIELD PROGRAMMABLE GATE ARRAY (FPGA)

## **SKRIPSI**

Diajukan Untuk Memenuhi Sebagian Persyaratan Memperoleh Gelar Sarjana Teknik

DISUSUN OLEH: HAFRIDA RAHMAH NIM. 0710630021-63

KEMENTERIAN PENDIDIKAN NASIONAL

UNIVERSITAS BRAWIJAYA

FAKULTAS TEKNIK

MALANG

2011

#### LEMBAR PERSETUJUAN

# IMPLEMENTASI MIKROPROSESOR 8085 DAN SISTEM MEMORI DALAM FIELD PROGRAMMABLE GATE ARRAY (FPGA)

### **SKRIPSI**

Diajukan Untuk Memenuhi Sebagian Persyaratan Memperoleh Gelar Sarjana Teknik

Disusun oleh:

HAFRIDA RAHMAH

NIM. 07106300021-63

Telah diperiksa dan disetujui oleh:

**Dosen Pembimbing I**

**Dosen Pembimbing II**

Moch. Rif'an, ST., MT.

NIP. 19710301 200012 1 001

Dr. Agung Darmawansyah, ST., MT.

NIP. 19721218 199903 1 002

#### **LEMBAR PENGESAHAN**

# IMPLEMENTASI MIKROPROSESOR 8085 DAN SISTEM MEMORI DALAM FIELD PROGRAMMABLE GATE ARRAY (FPGA)

Disusun oleh:

HAFRIDA RAHMAH

NIM. 0710630021-63

Skripsi ini telah diuji dan dinyatakan lulus pada tanggal **23 Desember 2011**

Majelis Penguji

<u>Ir. M. Julius St., MS.</u> NIP. 19540720 198203 1 002 <u>Ir. Ponco Siwindarto, M.Eng.Sc.</u> NIP. 19590304 198903 1 001

<u>Ir. Nurussa'adah, MT.</u> NIP. 19680706 199203 2 001

Mengetahui:

Ketua Jurusan Teknik Elektro

DR. Ir. Sholeh Hadi P., MS. NIP. 19580728 198701 1 001

#### **PENGANTAR**

Puji syukur kehadirat Allah SWT atas limpahan rahmat dan karuniaNya, penulis dapat menyelesaikan skripsi yang berjudul "Implementasi Mikroprosesor 8085 dan Sistem Memori Dalam *Field Programmable Gate Array (FPGA)*". Skripsi ini disusun sebagai persyaratan untuk memperoleh gelar Sarjana Teknik di Jurusan Teknik Elektro Universitas Brawijaya.

Penulis menyadari bahwa penyusunan skripsi ini tidak terlepas dari bantuan bebagai pihak. Oleh karena itu, dengan ketulusan dan kerendahan hati penulis menyampaikan terima kasih kepada:

- Ibu, Ayah, dan Nenek atas segala nasihat, kasih sayang, perhatian dan kesabarannya di dalam membesarkan dan mendidik penulis, serta telah banyak mendoakan kelancaran penulis hingga terselesaikannya skripsi ini,

- Kakak-kakak penulis yang banyak mendoakan hingga terselesaikannya skripsi ini,

- Bapak Dr. Ir. Sholeh Hadi Pramono, MS. selaku Ketua Jurusan Teknik Elektro Universitas Brawijaya,

- Bapak M. Aziz Muslim, ST., MT, Ph.D selaku Sekretaris Jurusan Teknik Elektro Universitas Brawijaya,

- Bapak M. Julius St, Ir., MS selaku Ketua Kelompok Dosen Keahlian Elektronika Jurusan Teknik Elektro Universitas Brawijaya,

- Bapak Moch. Rif'an, ST., MT. selaku Dosen Pembimbing I atas segala bimbingan, pengarahan, gagasan, ide, saran serta motivasi yang telah diberikan,

- Bapak Dr. Agung Darmawansyah, ST., MT selaku Dosen Pembimbing II atas segala bimbingan, pengarahan, saran, kritik, dan masukan yang telah diberikan,

- Staf Rekording, staf Pengajaran, dan staf Ruang Baca Jurusan Teknik Elektro yang telah membantu segala urusan penulis selama ini,

- Sahabat-sahabat penulis Fyta\_pytung, Dela, Rizki\_Kecil, Anno, Puput, Maul, dan Utari atas saran, semangat, pelajaran, pengalaman dan kebersamaan yang telah diberikan,

- GBEmate Yuli, Rizal, dan Anas atas waktu dan telinga kalian; classmate Doyot,

Inas, dan Tika; Mas Kanzi, Mas Arif, Yudo, Aka\_ct, Gladi, Pa'i, dan 2PM,

- Teman-teman Laboratorium SisDig, Workshop, pejuang PKM, dan Tim Roket Rintisan "Al-Fatih dan "E-Fly 63",

- Teman-teman CORE angkatan 2007 yang telah berbagi dalam hal duka maupun suka dengan penulis dan selalu mengajarkan arti kebersamaan,

- Seluruh teman-teman, senior serta semua pihak yang tidak mungkin untuk dicantumkan namanya satu-persatu, terima kasih banyak atas bantuan dan dukungannya.

Penulis menyadari bahwa tugas akhir ini masih belum sempurna. Oleh karena itu, penulis mengharapkan kritik dan saran untuk penyempurnaan tulisan di masa yang akan datang. Penulis berharap, semoga tugas akhir ini bermanfaat bagi kita semua.

## DAFTAR ISI

|       | ANTAR                                |    |

|-------|--------------------------------------|----|

|       | AR ISI                               |    |

|       | AR GAMBAR                            |    |

|       | AR TABEL                             |    |

| ABSTI | RAK                                  |    |

| BAB I |                                      | 1  |

| 1.1   | Latar Belakang                       | 1  |

| 1.2   | Rumusan Masalah                      | 2  |

| 1.3   | Ruang Lingkup                        | 2  |

| 1.4   | Tujuan                               | 2  |

| 1.5   | Sistematika Penulisan                |    |

| BAB I |                                      | 4  |

| 2.1   | Mikroprosesor                        | 4  |

| 2     | 2.1.1 Unit Kontrol                   |    |

| 2     | 2.1.2 Register                       | 5  |

|       | 2.1.3 ALU                            |    |

| 2,2   | Mikroprosesor 8085                   |    |

|       | 2.2.1 Siklus Prosesor                |    |

| 2.3   | Memori                               |    |

| 2.4   | Field-Programmable Gate Array (FPGA) | 11 |

|       | 2.4.1 Arsitektur FPGA                |    |

|       | II                                   |    |

|       |                                      |    |

| 3.1   | Studi Literatur                      |    |

| 3.2   | Penentuan Spesifikasi Rancangan      |    |

| 3.3   | Perancangan dan Perealisasian Sistem | 15 |

| 3.4   | Pengujian                            |    |

|       | 3.4.1 Pengujian Tiap Blok            |    |

| 3     | 3.4.2 Pengujian Keseluruhan Sistem   | 16 |

| B IV                                                                    |

|-------------------------------------------------------------------------|

| .1 Gambaran Kerja Sistem                                                |

| 4.1.1 Arsitektur Internal CPU                                           |

| 4.1.2 Alur Pemrosesan Instruksi                                         |

| 4.1.3 Hubungan Internal CPU, Register, dan Address Buffer da<br>8085 22 |

| 4.1.4 Arsitektur Keseluruhan Sistem                                     |

| 2 Instruksi-instruksi yang Dapat Dijalankan Sistem                      |

| 4.2.1 Instruksi Transfer Data                                           |

| 4.2.2 Instruksi Aritmatika dan Logika                                   |

| 4.2.3 Instruksi Percabangan                                             |

| 3 Perancangan Tiap Blok Penyusun Sistem                                 |

| 4.3.1 Unit Pembagi Clock                                                |

| 4.3.2 Unit ALU dan Status Flag.                                         |

| 4.3.3 Unit Bidirectional, Buffer, dan Dekoder                           |

| 4.3.4 Unit Input dan Unit Output                                        |

| 4.3.5 Unit Memori                                                       |

| 4.3.6 Penyusunan Blok Digital Menjadi Sistem Terpadu                    |

| 4 Implementasi Sistem ke Dalam IC FPGA Xilinx Spartar                   |

| 4.4.1 Pengaturan Relasi antara I/O Sistem dengan Kode Pin FP            |

| 4.4.2 Synthesize                                                        |

| 4.4.3 Mapping, Placing, dan Routing                                     |

| 4.4.4 Generate File Bitstream                                           |

| 4.4.5 Download File Bitstream                                           |

| 8 V                                                                     |

| 1 Pengujian Clock                                                       |

| 5.1.1 Tujuan Pengujian                                                  |

| 5.1.2 Peralatan Pengujian                                               |

| 5.1.3 Prosedur Pengujian                                                |

| 5.1.4 Data dan Analisis Hasil Pengujian Clock                           |

| 5.2.2 Peralatan Pengujian                         | 66 |

|---------------------------------------------------|----|

| 5.2.3 Prosedur Pengujian                          |    |

| 5.2.4 Data Hasil Pengujian Unit Input Output      | 68 |

| 5.2.5 Analisis Hasil Pengujian Unit Input Output  |    |

| 5.3 Pengujian Memori                              | 72 |

| 5.3.1 Tujuan Pengujian                            | 72 |

| 5.3.2 Peralatan Pengujian                         | 72 |

| 5.3.3 Prosedur Pengujian                          | 72 |

| 5.3.4 Data Hasil Pengujian Unit Memori            | 75 |

| 5.3.5 Analisis Hasil Pengujian Unit Memori        | 77 |

| 5.4 Pengujian Unit Bidirectional                  | 77 |

| 5.4.1 Tujuan Pengujian                            | 77 |

| 5.4.2 Peralatan Pengujian                         | 77 |

| 5.4.3 Prosedur Pengujian                          | 78 |

| 5.4.4 Data Hasil Pengujian Unit Bidirectional     | 81 |

| 5.4.5 Analisis Hasil Pengujian Unit Bidirectional | 82 |

| 5.5 Pengujian Unit Buffer                         | 83 |

| 5.5.1 Tujuan Pengujian                            | 83 |

| 5.5.2 Peralatan Pengujian                         | 84 |

| 5.5.3 Prosedur Pengujian                          |    |

| 5.5.4 Data Hasil Pengujian Unit Buffer            | 85 |

| 5.5.5 Analisis Hasil Pengujian Unit Buffer        |    |

| 5.6 Pengujian Unit Dekoder                        | 86 |

| 5.6.1 Tujuan Pengujian                            | 86 |

| 5.6.2 Peralatan Pengujian                         | 86 |

| 5.6.3 Prosedur Pengujian                          |    |

| 5.6.4 Data Hasil Pengujian Unit Dekoder           | 87 |

| 5.6.5 Analisis Hasil Pengujian Unit Dekoder       | 88 |

| 5.7 Pengujian ALU                                 | 88 |

| 5.7.1 Tujuan Pengujian                            |    |

| 5.7.2 Peralatan Pengujian                         |    |

| 5.7.3 Prosedur Pengujian                          | 88 |

| 5.7.4 Data Hasil Pengujian Unit ALU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 90  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

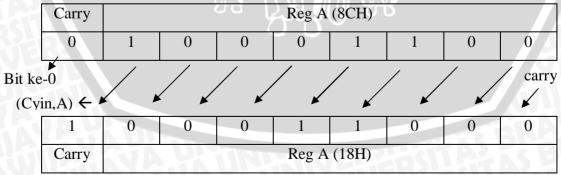

| 5.7.5 Analisis Hasil Pengujian Output ALU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 5.7.6 Analisis Hasil Pengujian Register Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 5.8 Pengujian Unit Kontrol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 100 |

| 5.8.1 Tujuan Pengujian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100 |

| 5.8.2 Peralatan Pengujian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 100 |

| 5.8.3 Prosedur Pengujian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100 |

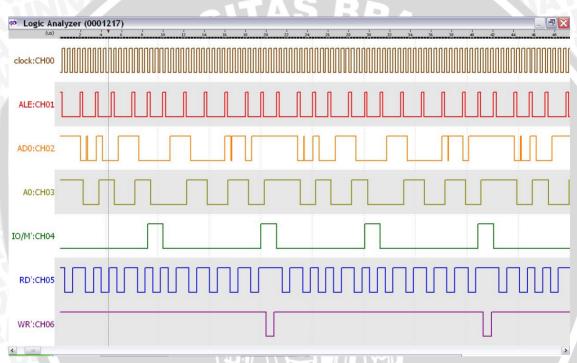

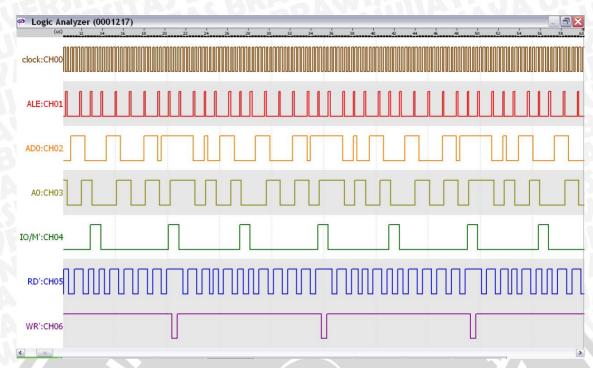

| 5.8.4 Data Hasil Pengujian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 5.8.5 Analisis Hasil Pengujian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 112 |

| 5.9 Komparasi Modul Mikroprosesor 8085 dengan Sistem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 113 |

| 5,9.1 Tujuan Pengujian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 113 |

| 5.9.2 Peralatan Pengujian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 113 |

| 5.9.3 Prosedur Pengujian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 113 |

| 5.9.4 Data Hasil Pengujian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 115 |

| BAB VI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 118 |

| 6.1 Kesimpulan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 118 |

| 6.2 Saran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 119 |

| DAFTAR PUSTAKA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 120 |

| LAMPIRAN YA A TIMEN YA KANTAN YA KAN | 121 |

## DAFTAR GAMBAR

| Gambar 2.1 (a) Intel 4004, (b) inti 4004                                      |    |

|-------------------------------------------------------------------------------|----|

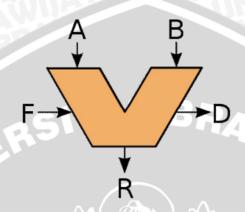

| Gambar 2.2 Simbol ALU                                                         | 6  |

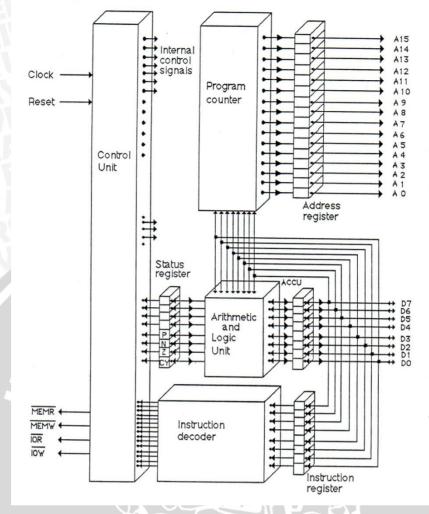

| Gambar 2.3 Arsitektur Mikroprosesor 8085                                      |    |

| Gambar 2.4 Bentuk fisik FPGA                                                  | 11 |

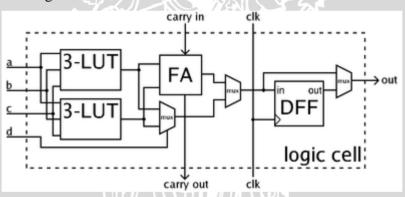

| Gambar 2.5 Contoh Sebuah Sel Logika                                           | 12 |

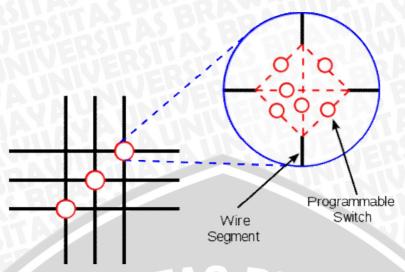

| Gambar 2.6 Topologi Switch Box                                                | 13 |

| Gambar 4.1 Arsitektur Internal CPU                                            | 19 |

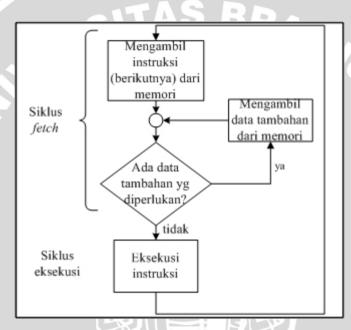

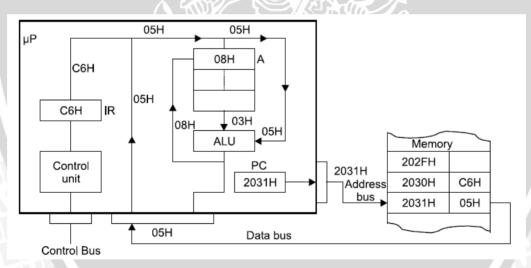

| Gambar 4.2 Alur Pemrosesan Instruksi pada Mikroprosesor                       | 20 |

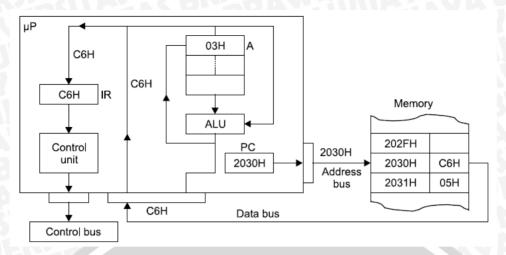

| Gambar 4.3 Siklus Fetch: Peletakan Byte Pertama (Opcode) kedalam Register Ins |    |

| Gambar 4.4 Pengeksekusian Instruksi: Pembacaan Byte Kedua dari Memori         | 21 |

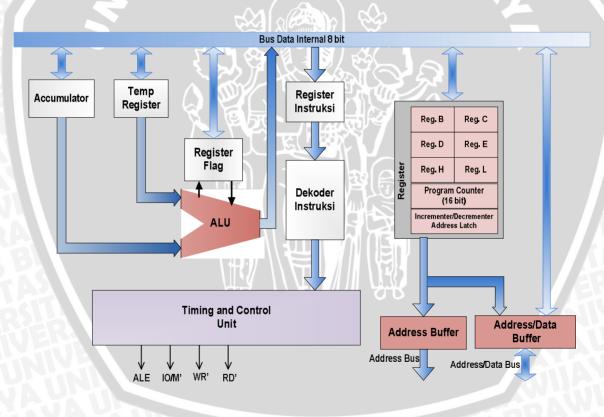

| Gambar 4.5 Arsitektur Internal Mikroprosesor 8085                             | 23 |

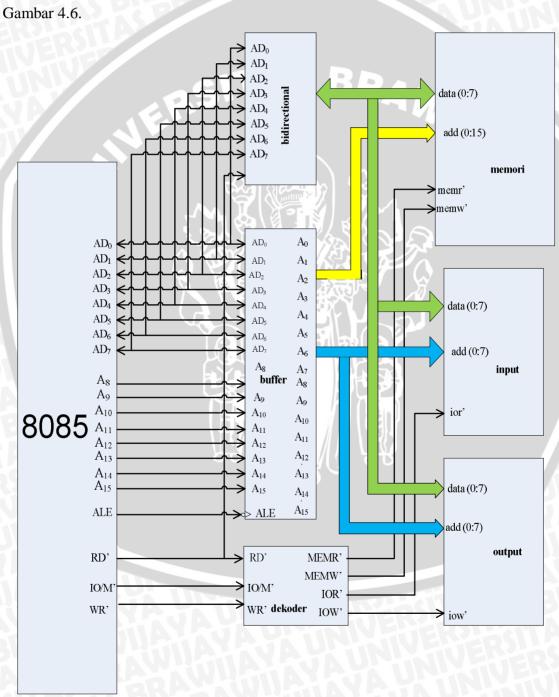

| Gambar 4.6 Keseluruhan Sistem Modul Mikroprosesor 8085                        |    |

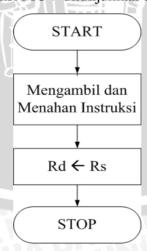

| Gambar 4.7 Diagram Alir Instruksi MOV                                         | 26 |

| Gambar 4.8 Diagram Alir Instruksi MVI                                         | 28 |

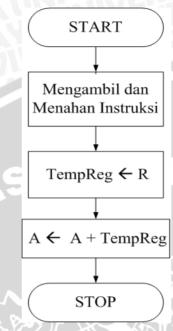

| Gambar 4.9 Diagram Alir Instruksi ADD                                         |    |

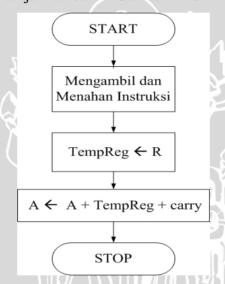

| Gambar 4.10 Diagram Alir Instruksi ADC                                        | 31 |

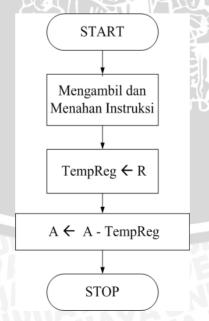

| Gambar 4.11 Diagram Alir Instruksi SUB                                        |    |

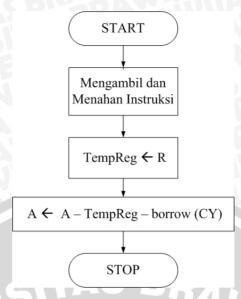

| Gambar 4.12 Diagram Alir Instruksi SBB                                        | 34 |

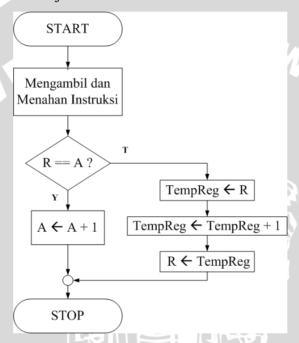

| Gambar 4.13 Diagram Alir Instruksi INR                                        | 35 |

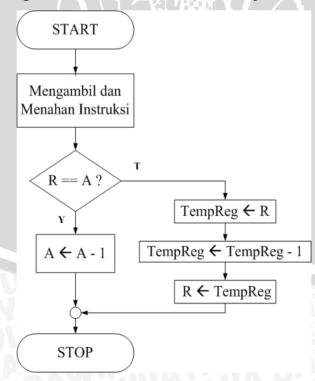

| Gambar 4.14 Diagram Alir Instruksi DCR                                        | 36 |

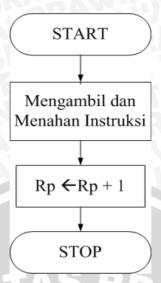

| Gambar 4.15 Diagram Alir Instruksi INX                                        | 38 |

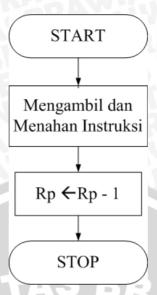

| Gambar 4.16 Diagram Alir Instruksi DCX                                        | 39 |

| Gambar 4.17 Diagram Alir Instruksi ANA                                        | 40 |

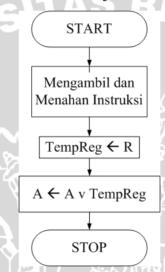

| Gambar 4.18 Diagram Alir Instruksi ORA                                        | 41 |

| Gambar 4.19 Diagram Alir Instruksi XRA                                        | 42 |

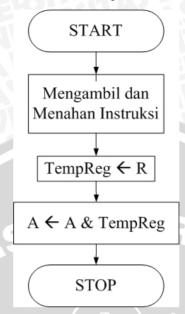

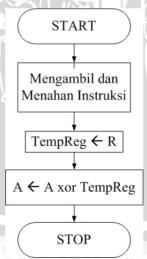

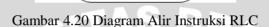

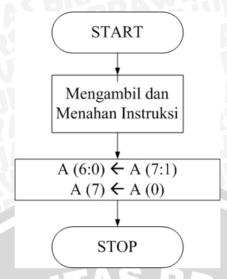

| Gambar 4.20 Diagram Alir Instruksi RLC                                        |    |

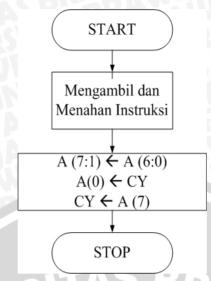

| Gambar 4.21 Diagram Alir Instruksi RRC                                        | 45 |

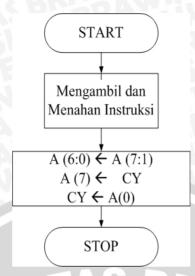

| Gambar 4.22 Diagram Alir Instruksi RAL                                        | 46 |

| Gambar 4.23 Diagram Alir Instruksi RAR                                        | 47 |

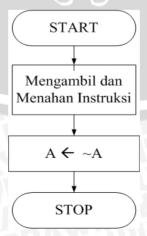

| Gambar 4.24 Diagram Alir Instruksi CMA                                        |    |

| Gambar 4.25 Diagram Alir Instruksi JMP                                        | 48 |

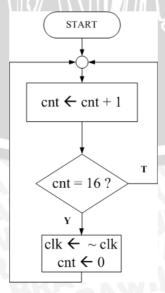

| Gambar 4.26 Diagram Alir Unit Sistem Clock                                           |

|--------------------------------------------------------------------------------------|

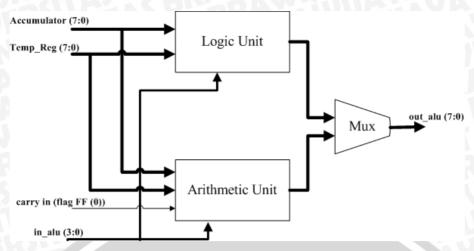

| Gambar 4.27 Diagram Blok Rancangan ALU51                                             |

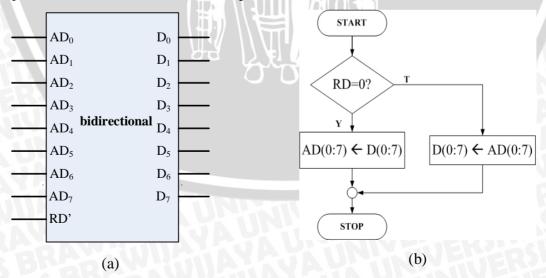

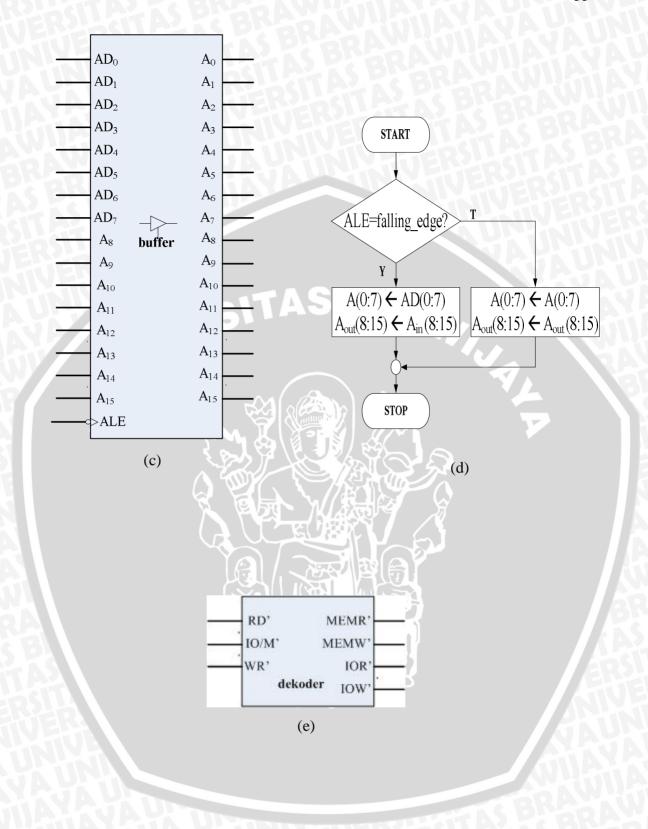

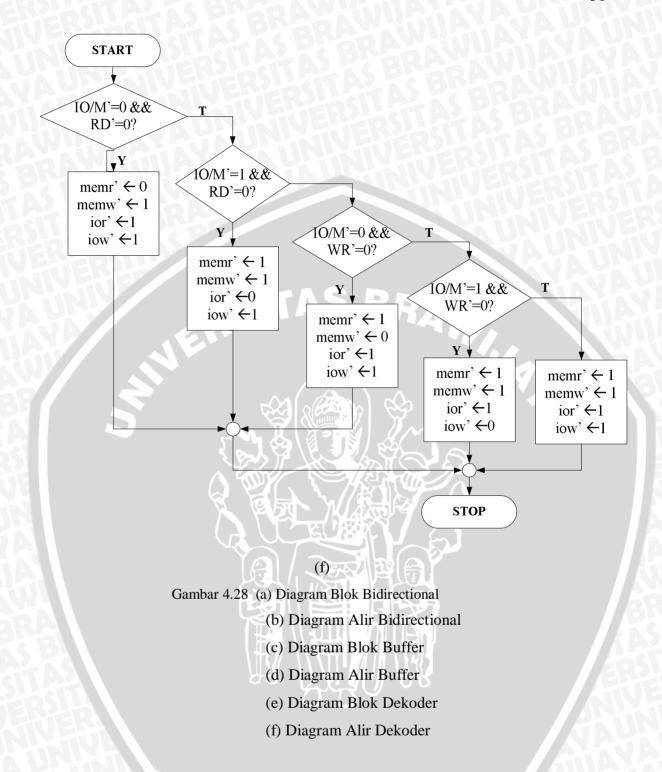

| Gambar 4.28 (a) Diagram Blok Bidirectional                                           |

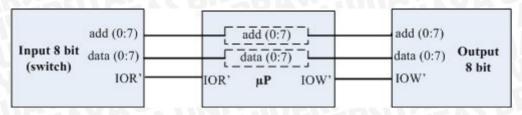

| Gambar 4.29 Diagram Blok Unit Input dan Output                                       |

| Gambar 4.30 Diagram Blok Unit Memori                                                 |

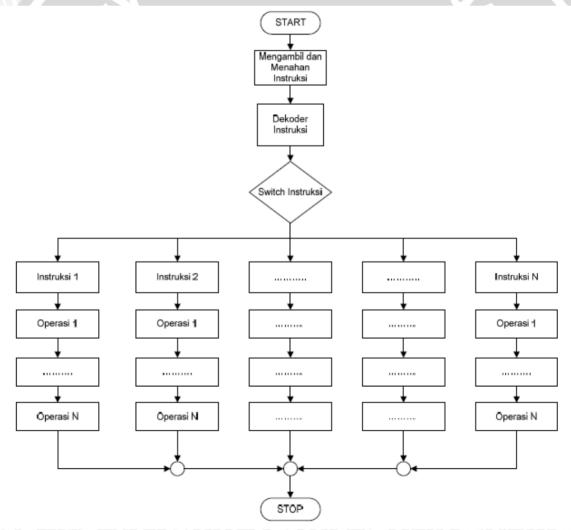

| Gambar 4.31 Diagram Alir Unit Kontrol                                                |

| Gambar 4. 32 Konfigurasi Pin FPGA yang Digunakan Sebagai I/O Sistem62                |

| Gambar 5. 1 Perangkat Pengujian Clock                                                |

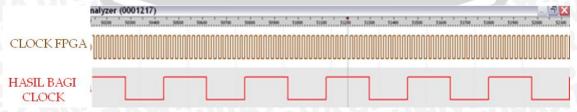

| Gambar 5. 2 Tampilan Clock FPGA dan Hasil Pembagian Clock                            |

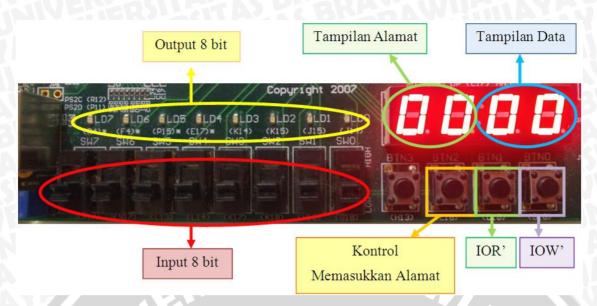

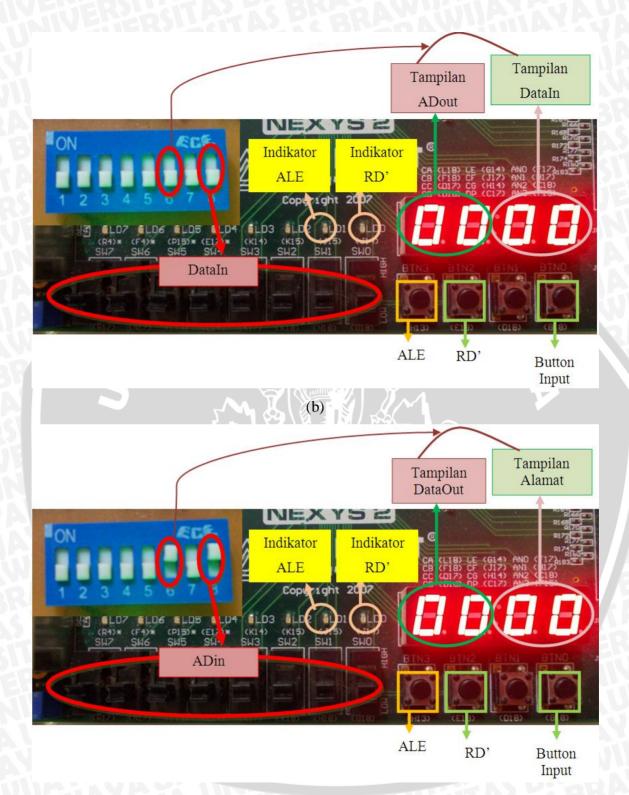

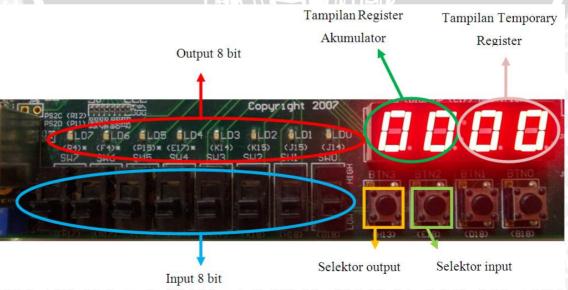

| Gambar 5. 3 Penentuan Input, Output, dan Kontrol pada Pengujian Unit Input Output 67 |

| Gambar 5. 4 Menentukan Alamat dengan Menekan Button "Active Address"67               |

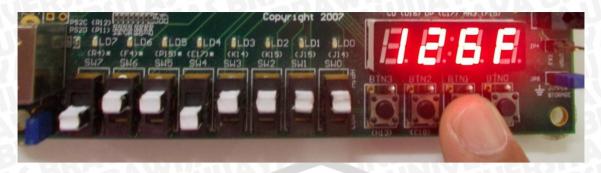

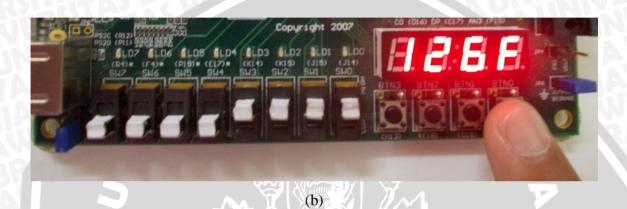

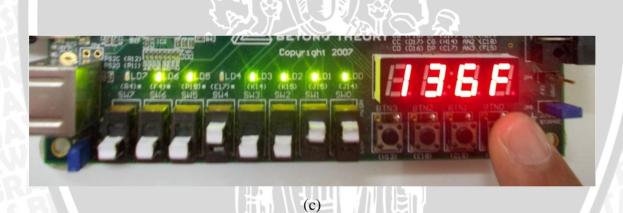

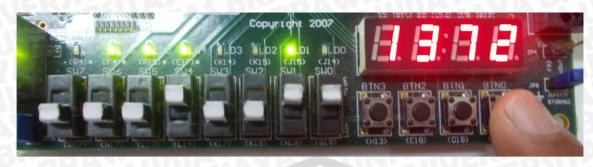

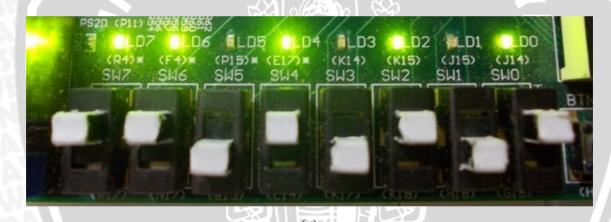

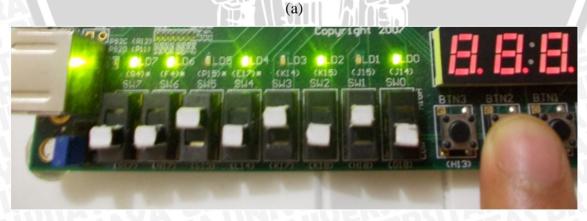

| Gambar 5. 5 (a) Hasil Pengujian Unit Input Output pada Tabel 16 no. 271              |

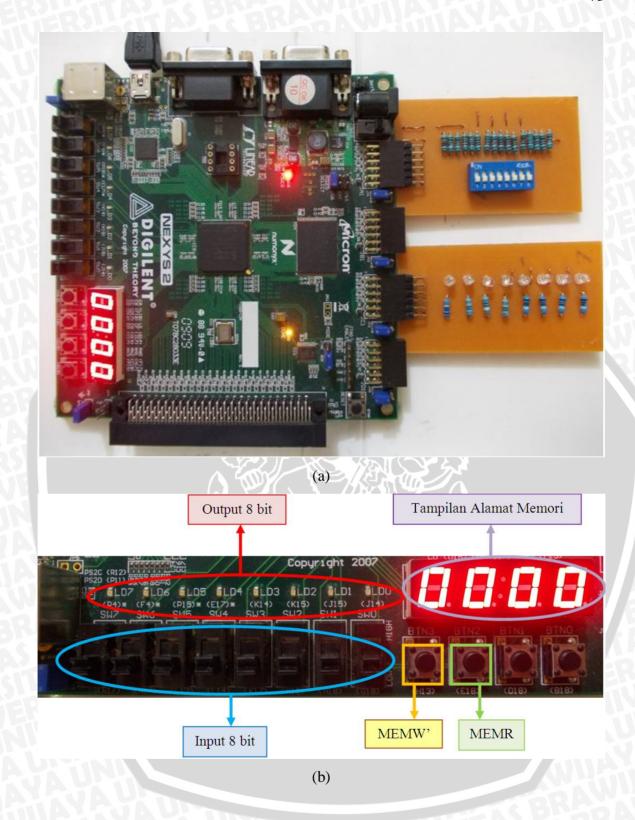

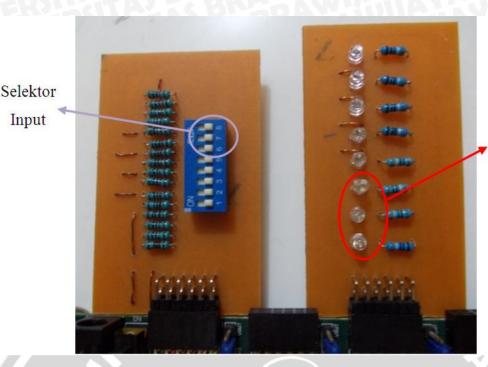

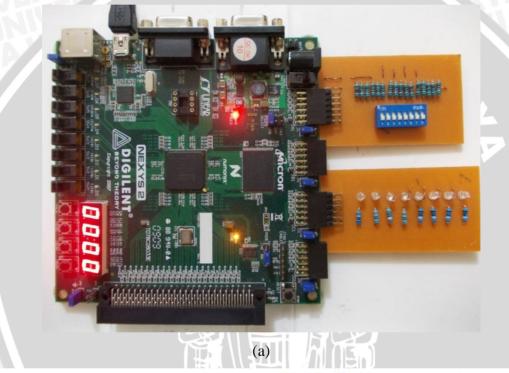

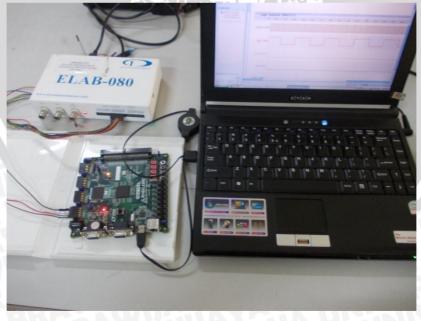

| Gambar 5. 6 (a) Modul Pengujian Menyeluruh                                           |

| Gambar 5. 7 (a) Hasil Pengujian Unit Memori pada Tabel 17 no. 1                      |

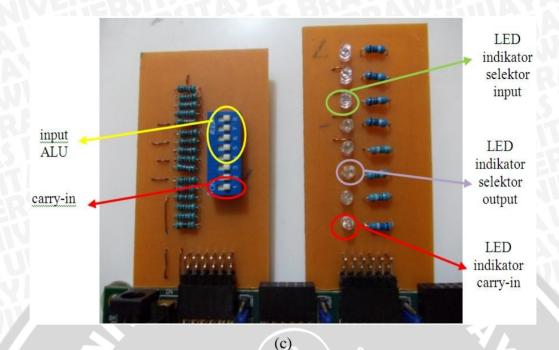

| Gambar 5. 8 (a) Modul Pengujian Menyeluruh80                                         |

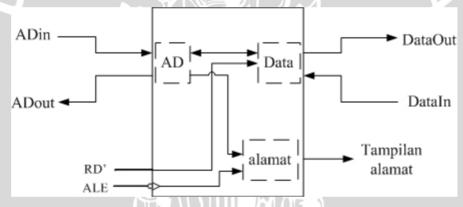

| Gambar 5. 9 Diagram Blok Pengujian Bidirectional80                                   |

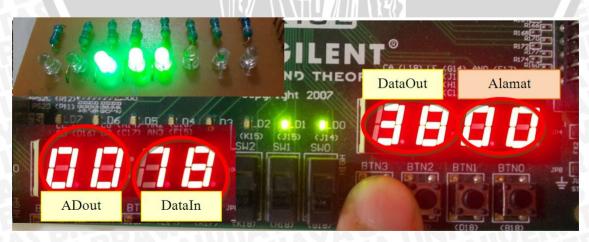

| Gambar 5. 10 (a) Hasil Pengujian Unit Bidirectional pada Tabel 18 no. 182            |

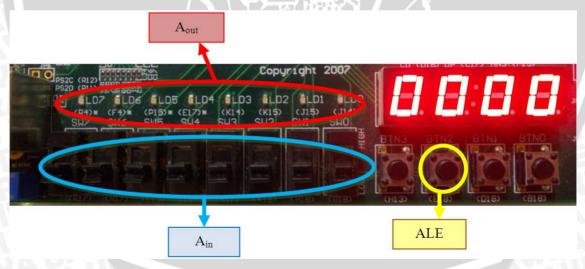

| Gambar 5. 11 Penetapan Port Ain dan Aout                                             |

| Gambar 5. 12 (a) Hasil Pengujian Unit Buffer pada Tabel 19 no. 385                   |

| Gambar 5. 13 Penentuan Port-port untuk Pengujian Unit Dekoder                        |

| Gambar 5. 14 (a) Hasil Pengujian Unit Input Output pada Tabel 20 no. 1,              |

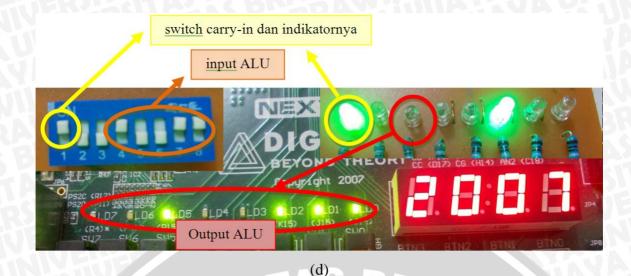

| Gambar 5.15 (a) Modul Pengujian Menyeluruh90                                         |

| Gambar 5. 16 Hasil Pengujian Unit ALU pada Tabel 293                                 |

| Gambar 5.17 Perangkat Pengujian Unit Kontrol                                         |

| Gambar 5. 18 Perangkat Pengujian Menggunakan ModulKit                                |

| Gambar 5. 19 Perangkat Pengujian Menggunakan FPGA                                    |

| Gambar 5. 20 Hasil Pengujian Saat Menggunakan Modulkit Praktikum                     |

| Mikroprosesor 8085                                                                   |

| Gambar 5. 21 Hasil Pengujian Saat Menggunakan Rancangan Sistem dalam FPGA116         |

## DAFTAR TABEL

| Tabel 1 Instruksi MOV Rd,Rs dan Op-code                                     | 27   |

|-----------------------------------------------------------------------------|------|

| Tabel 2 Instruksi MVI Rd,n dan Op-code                                      |      |

| Tabel 3 Instruksi ADD dan Op-code                                           | 30   |

| Tabel 4 Instruksi ADC dan Op-code                                           | 32   |

| Tabel 5 Instruksi SUB dan Op-code                                           | 33   |

| Tabel 6 Instruksi SBB dan Op-code                                           | 34   |

| Tabel 7 Instruksi INR dan Op-code                                           | 36   |

| Tabel 8 Instruksi DCR dan Op-code                                           | 37   |

| Tabel 8 Instruksi DCR dan Op-code                                           | 38   |

| Tabel 10 Instruksi DCX dan Op-code                                          | 39   |

| Tabel 11 Instruksi ANA dan Op-code                                          | 40   |

| Tabel 12 Instruksi ORA dan Op-code                                          |      |

| Tabel 13 Instruksi XRA dan Op-code                                          | 43   |

| Tabel 14 Daftar Kebenaran Unit ALU                                          | 51   |

| Tabel 15 Daftar Kebenaran Status Flag.                                      | 52   |

| Tabel 16 Slices, slice flip-flops, 4 input LUTs, dan BUFGMUXs Penyusun Sist | em63 |

| Tabel 17 Data Hasil Pengujian Unit Input Output                             |      |

| Tabel 18 Data Hasil Pengujian Unit Memori                                   | 75   |

| Tabel 19 Data Hasil Pengujian Unit Bidirectional                            |      |

| Tabel 20 Data Hasil Pengujian Unit Buffer                                   |      |

| Tabel 21 Data Hasil Pengujian Unit Dekoder                                  |      |

| Tabel 22 Data Hasil Pengujian Unit ALU                                      | 91   |

| Tabel 23 Penjabaran Status Register Flag                                    | 99   |

| Tabel 24 Hasil Pengujian Program 1                                          | 103  |

| Tabel 25 Hasil Pengujian Program 2                                          | 103  |

| Tabel 26 Hasil Pengujian Program 3                                          | 104  |

| Tabel 27 Hasil Pengujian Program 4                                          | 104  |

| Tabel 28 Penjabaran Siklus Clock (States) pada Instruksi MVI A,55           | 105  |

| Tabel 29 Penjabaran Siklus Clock (States) pada Instruksi MOV C,B            | 105  |

| Tabel 30 Penjabaran Siklus Clock (States) pada Instruksi INR A              |      |

| Tabel 31 Penjabaran Siklus Clock (States) pada Instruksi ADD B              | 106  |

| Tabel 32 Penjabaran Siklus Clock (States) pada Instruksi SUB B              | 107  |

|                                                                             |      |

| Tabel 33 Penjabaran Siklus Clock (States) pada Instruksi RLC    | .107  |

|-----------------------------------------------------------------|-------|

| Tabel 34 Penjabaran Siklus Clock (States) pada Instruksi INX B  | . 108 |

| Tabel 35 Siklus Clock (States) pada Instruksi JMP 0002          | .109  |

| Tabel 36 Penjabaran Siklus Clock (States) pada Instruksi IN 12  | .110  |

| Tabel 37 Penjabaran Siklus Clock (States) pada Instruksi OUT 13 | .111  |

#### **ABSTRAK**

**Hafrida Rahmah,** Jurusan Teknik Elektro Fakultas Teknik Universitas Brawijaya, Desember 2011, *Implementasi Mikroprosesor 8085 dan Sistem Memori Dalam Field Programmable Gate Array (FPGA)*, Dosen Pembimbing: Moch. Rif'an, ST., MT. dan Dr. Agung Darmawansyah ST., MT.

Mikroprosesor adalah sebagai pengontrol atau pengolah utama dalam suatu rangkaian elektronik. Kecenderungan terhadap penggunaan mikroprosesor bertahan cukup lama hingga dikembangkannya mikrokontroler. Namun, penggunaan mikroprosesor sebagai dasar pembelajaran masih tetap dikembangkan dan belum dapat tergantikan. Kebutuhan akan mikroprosesor untuk pembelajaran di institusi berbanding terbalik dengan ketersediaan mikroprosesor dan penunjangnya saat ini contohnya pada praktikum sistem digital di Laboratorium Sistem Digital TEUB. Oleh karena itu, diperlukan pengganti mikroprosesor 8085 yang tetap dapat berfungsi sebagaimana seperti mikroprosesor 8085 sehingga dirancanglah sistem pengganti mikroprosesor yang ditanamkan dalam FPGA.

Sistem pengganti ini juga harus mempunyai memori dan unit input output agar dapat langsung digunakan tanpa penambahan perangkat lain. Mikroprosesor 8085 ini harus dapat digunakan untuk memproses suatu instruksi berdasar set instruksi 8085 dengan sinyal kontrol yang dimilikinya,memiliki frekuensi clock sesuai rentang besaran yang dapat dimiliki, dapat membaca maupun menulis data ke unit luar yaitu unit input output dan memori. Hasil pengujian menunjukkan bahwa sistem mikroprosesor 8085 dapat memproses instuksi-instruksi yang diperintahkan sesuai dengan beberapa instruksi dalam set instruksi 8085, memiliki keluaran sinyal kontrol yang sesuai dan frekuensi bekerja sesuai dengan range maksimum frekuensi mikroprosesor 8085 yaitu 3,25MHz sehingga kinerja lebih cepat jika dibandingkan modulkit praktikum mikroprosesor 8085 yang ada yaitu 2 MHz dan juga dapat menggantikan modul praktikum yang telah ada.

Kata kunci: Mikroprosesor, Clock, Sinyal kontrol, Memori, FPGA

### BAB I PENDAHULUAN

#### 1.1 Latar Belakang

Sejak awal perkembangannya hingga saat ini, teknologi digital menjadi salah satu teknologi yang berkembang begitu pesat. Hampir semua teknologi analog digantikan dengan teknologi digital. Perangkat digital seperti pemutar MP3 tersusun atas sistem yang kompleks yang biasa dikenal dengan *integrated circuit (IC)*. Salah satu perkembangan IC yang dikenal secara umum untuk pembelajaran suatu teknologi digital yang bekerja dengan program adalah mikroprosesor.

Mikroprosesor adalah salah satu perkembangan teknologi digital. Mikroprosesor adalah sebuah chip (IC) yang bekerja dengan program. Fungsi mikroprosesor adalah sebagai pengontrol atau pengolah utama dalam suatu rangkaian elektronik. Mikroprosesor biasa disebut juga CPU (Central Processing Unit). Kecenderungan terhadap penggunaan mikroprosesor bertahan cukup lama hingga dikembangkannya mikrokontroler. Namun, penggunaan mikroprosesor sebagai dasar pembelajaran masih tetap dikembangkan dan belum dapat tergantikan.

Kebutuhan akan mikroprosesor untuk pembelajaran di institusi berbanding terbalik dengan ketersediaan mikroprosesor dan penunjangnya saat ini. Sebagai contoh, praktikum mata kuliah mikroprosesor yang menggunakan mikroprosesor 8085 yang digunakan di beberapa laboratorium institusi perguruan tinggi semakin berkurang, padahal ketersediaan mikroprosesor ini di pasaran sudah tidak ada. Oleh karena itu, diperlukan pengganti mikroprosesor 8085 yang tetap dapat berfungsi sebagaimana seperti mikroprosesor 8085.

Sistem pengganti mikroprosesor 8085 jika diciptakan dengan proses produksi *IC* (*integrated circuit*) akan sangat kompleks, membutuhkan biaya, dan membutuhkan waktu pengerjaan yang lama sehinga hampir tidak memungkin bagi kita untuk membuatnya. Namun, saat ini telah ditemukan teknologi *PLD* (*programmable logic device*) yang salah satu contohnya adalah FPGA yaitu sebuah teknologi integrasi yang mampu diprogram menjadi suatu rangkaian sesuai dengan yang kita inginkan. Dengan adanya teknologi PLD maka sistem pengganti mikroprosesor 8085 dapat dirancang hingga berfungsi sebagaimana seperti mikroprosesor 8085.

#### 1.2 Rumusan Masalah

Berdasarkan latar belakang yang telah dikemukakan sebelumnya, dapat dirumuskan permasalahan sebagai berikut:

- 1) Bagaimana arsitektur mikroprosesor 8085 yang akan dirancang dalam FPGA sebagai media implementasi sistem.

- 2) Bagaimana sistem memori yang dapat kompatibel dengan mikroprosesor 8085.

- 3) Bagaimana rancangan sistem penunjang dibutuhkan yang menghubungkan mikroprosesor dengan memori dan unit luar mikroprosesor.

- 4) Apakah sistem dapat digunakan sesuai dengan penggunaan mikroprosesor 8085 meliputi beberapa instruksi dalam instruction set mikroprosesor 8085.

#### 1.3 Ruang Lingkup

Mengacu pada permasalahan yang telah dirumuskan, maka hal-hal yang berkaitan dengan rancangan akan diberi batasan sebagai berikut:

- Membahas bagaimana sistem mikroprosesor 8085 bekerja.

- Membahas bagaimana sistem memori dapat digunakan dengan mikroprosesor 8085.

- 3) Intruksi yang dapat dijalankan atau dieksekusi menggunakan instruksi-instruksi yang sering digunakan dalam praktikum mikroprosesor 8085.

- Tidak membahas cara penulisan bahasa hardware yang akan digunakan pada sistem mikroprosesor 8085.

#### 1.4 Tujuan

Penelitian ini bertujuan untuk merancang pengganti mikroprosesor 8085 yang sesuai dengan arsitektur mikroprosesor 8085 dan sistem memori sebagai pengganti alat praktikum dasar teknologi digital sehingga pembelajaran tentang teknologi digital dapat terus berlangsung.

#### 1.5 Sistematika Penulisan

Skripsi ini terdiri dari enam bab dengan sistematika pembahasan sebagai berikut:

#### BAB I Pendahuluan

Membahas latar belakang, rumusan masalah, ruang lingkup, tujuan, dan sistematika pembahasan.

#### BAB II Tinjauan Pustaka

Membahas teori-teori yang mendukung dalam perancangan dan pembuatan alat, yang meliputi : arsitektur mikroprosesor 8085, arsitektur memori, perangkat modul praktikum mikroprosesor 8085 dan spesifikasinya, Field Programmable Gate Array.

#### BAB III Metodologi Penulisan

Membahas metode penelitian dan perencanaan sistem.

#### **BAB IV** Perancangan dan Pembuatan Alat

Membahas perancangan sistem mikroprosesor, jalannya sistem mikroprosesor beserta koordinasi mikroprosesor dengan unit-unit tambahan, serta perancangan tiap blok unit-unit penyusun sistem mikroprosesor, sistem bidirectional buffer dekoder, memori, serta input output.

#### BAB V Pengujian dan Analisis

Membahas hasil pengujian sistem untuk tiap-tiap blok dan secara keseluruhan.

#### Bab VI Kesimpulan dan Saran

Membahas kesimpulan perancangan ini dan saran-saran yang diperlukan untuk pengembangan selanjutnya.

### BAB II TINJAUAN PUSTAKA

Bagian yang akan dibahas dalam sistem mikroprosesor 8085 dan memori ini adalah gambaran umum tentang mikroprosesor, mikroprosesor 8085, karakteristik memori yang dapat diakses oleh mikroprosesor 8085, serta FPGA sebagai devais perancangan program sistem mikroprosesor 8085.

#### 2.1 Mikroprosesor

Mikroprosesor adalah seluruh atau sebagian besar representasi fungsi dari central processing unit (CPU) yang merupakan sebuah "mesin" pemproses yang dibuat dengan menggunakan teknologi mikro dan terintegrasi dalam sebuah integrated circuit (IC). Mikroprosessor didesain untuk melakukan operasi-operasi aritmatika dan logika. Operasi-operasi ini dilakukan di dalam mikroprosessor dengan bantuan beberapa blok penyimpan data yang disebut dengan register. Mikroprosessor pada umumnya dapat melakukan operasi penjumlahan, pengurangan, perbandingan dua angka, dan mengatur perpindahan suatu angka dari suatu tempat ke tempat yang lain. Operasi-operasi tersebut adalah hasil dari sebuah set of instruction yang juga merupakan bagian dari mikroprosessor.

Mikroprosessor yang pertama kali dibuat adalah mikroprosessor 4004 yang dibuat oleh Intel pada awal tahun 1970an. Mikroprosessor ini digunakan untuk kalkulator elektronik yang masin menggunakan 4-bit aritmatika BCD (binary code decimal). Dengan adanya general-purpose microprocessor pertama ini, perkembangan teknologi di bidang pemprosessan data menjadi sangat pesat. Pembuatan-pembuatan mikroprosessor 8 hingga 16 bit-pun mengawali kemajuan mikrokomputer di pertengahan era 70an. Gambar 2.1 menunjukkan bentuk fisik, inti die, dan schematic dari Intel 4004.

(a)

Gambar 2.1 (a) Intel 4004, (b) inti 4004

Mikroprosessor bekerja dengan cara menjalankan dan mengatur perpindahan data pada jalur data (data bus) dan serta memproses data yang didapatkan tergantung dari instruksi yang ada. Pengaturan dan pengkontrolan ini dilakukan dengan memanfaatkan jalur alamat dan jalur kontrol. Jalur kontrol berfungsi untuk membedakan kondisi perpindahan data (membaca atau menulis) dan sekaligus membedakan peripheral yang akan di kontrol (memori, rom,atau I/O dan lain sebagainya). Sedangkan jalur alamat berfungsi untuk mendefinisikan secara spesifik letak data yang akan diproses, seperti alamat dalam memori, I/O dan lain sebagainya.

Komponen mikroprosesor atau yang lebih mudah kita sebut dengan CPU (central processing unit) terbagi menjadi beberapa macam, yaitu sebagai berikut:

### 2.1.1 Unit Kontrol

Unit kontrol yang mampu mengatur jalannya program. Komponen ini sudah pasti terdapat dalam semua CPU.CPU bertugas mengontrol komputer sehingga terjadi sinkronisasi kerja antar komponen dalam menjalankan fungsi-fungsi operasinya. termasuk dalam tanggung jawab unit kontrol adalah mengambil intruksi-intruksi dari memori utama dan menentukan jenis instruksi tersebut. Bila ada instruksi untuk perhitungan aritmatika atau perbandingan logika, maka unit kendali akan mengirim instruksi tersebut ke ALU. Hasil dari pengolahan data dibawa oleh unit kendali ke memori utama lagi untuk disimpan, dan pada saatnya akan disajikan ke alat output. Dengan demikian tugas dari unit kendali ini adalah:

- 1) Mengatur dan mengendalikan alat-alat input dan output.

- 2) Mengambil instruksi-instruksi dari memori utama.

- 3) Mengambil data dari memori utama (jika diperlukan) untuk diproses.

- 4) Mengirim instruksi ke ALU bila ada perhitungan aritmatika atau perbandingan logika serta mengawasi kerja dari ALU.

- 5) Menyimpan hasil proses ke memori utama.

#### 2.1.2 Register

Register merupakan alat penyimpanan kecil yang mempunyai kecepatan akses cukup tinggi, yang digunakan untuk menyimpan data dan/atau instruksi yang sedang diproses. Memori ini bersifat sementara, biasanya digunakan untuk menyimpan data saat di olah ataupun data untuk pengolahan selanjutnya. Secara analogi, register ini dapat diibaratkan sebagai ingatan di otak bila kita melakukan pengolahan data secara manual, sehingga otak dapat diibaratkan sebagai CPU, yang berisi ingatan-ingatan,

satuan kendali yang mengatur seluruh kegiatan tubuh dan mempunyai tempat untuk melakukan perhitungan dan perbandingan logika.

#### 2.1.3 ALU

ALU unit yang bertugas untuk melakukan operasi aritmetika dan operasi logika berdasar instruksi yang ditentukan. Bentuk ALU biasanya digambarkan dalam bentuk V, Gambar 2.2 menunjukkan simbol sebuah ALU.

Gambar 2.2 Simbol ALU

Sumber: http://upload.wikimedia.org/wikipedia/commons/thumb/8/82/ALU\_symbol.svg/300px-ALU\_symbol.svg.png

ALU sering di sebut mesin bahasa karena bagian ini ALU terdiri dari dua bagian, yaitu unit aritmatika memiliki spesifikasi tugas tersendiri. Tugas utama dari ALU adalah melakukan semua perhitungan aritmatika (matematika) yang terjadi sesuai dengan instruksi program. ALU melakukan semua operasi aritmatika dengan dasar penjumlahan sehingga sirkuit elektronik yang digunakan disebut adder.

#### Cara Kerja CPU

Saat data dan/atau instruksi dimasukkan ke processing-devices, pertama sekali diletakkan di RAM (melalui Input-storage); apabila berbentuk instruksi ditampung oleh Control Unit di Program-storage, namun apabila berbentuk data ditampung di Working-storage). Jika register siap untuk menerima pengerjaan eksekusi, maka Control Unit akan mengambil instruksi dari Program-storage untuk ditampungkan ke Instruction Register, sedangkan alamat memori yang berisikan instruksi tersebut ditampung di Program Counter. Sedangkan data diambil oleh Control Unit dari Working-storage untuk ditampung di General-purpose register (dalam hal ini di Operand-register). Jika berdasar instruksi pengerjaan yang dilakukan adalah arithmatika dan logika, maka ALU akan mengambil alih operasi untuk mengerjakan berdasar instruksi yang ditetapkan. Hasilnya ditampung di Accumulator. Apabila hasil pengolahan telah selesai, maka

Control Unit akan mengambil hasil pengolahan di Accumulator untuk ditampung kembali ke Working-storage. Jika pengerjaan keseluruhan telah selesai, maka Control Unit akan menjemput hasil pengolahan dari Working-storage untuk ditampung ke Output-storage. Lalu selanjutnya dari *Outputstorage*, hasil pengolahan akan ditampilkan ke output-devices.

#### **Fungsi CPU**

CPU berfungsi seperti kalkulator, hanya saja CPU jauh lebih kuat daya pemrosesannya. Fungsi utama dari CPU adalah melakukan operasi aritmatika dan logika terhadap data yang diambil dari memori atau dari informasi yang dimasukkan melalui beberapa perangkat keras, seperti papan ketik, pemindai, tuas kontrol, maupun tetikus. CPU dikontrol menggunakan sekumpulan instruksi perangkat lunak komputer. Perangkat lunak tersebut dapat dijalankan oleh CPU dengan membacanya dari media penyimpan, seperti cakram keras, disket, cakram padat, maupun pita perekam. Instruksiinstruksi tersebut kemudian disimpan terlebih dahulu pada memori fisik (RAM), yang mana setiap instruksi akan diberi alamat unik yang disebut alamat memori. Selanjutnya, CPU dapat mengakses data-data pada RAM dengan menentukan alamat data yang dikehendaki.

Saat sebuah program dieksekusi, data mengalir dari RAM ke sebuah unit yang disebut dengan bus, yang menghubungkan antara CPU dengan RAM. Data kemudian didekode dengan menggunakan unit proses yang disebut sebagai pendekoder instruksi yang sanggup menerjemahkan instruksi. Data kemudian berjalan ke unit aritmatika dan logika (ALU) yang melakukan kalkulasi dan perbandingan. Data bisa jadi disimpan sementara oleh ALU dalam sebuah lokasi memori yang disebut dengan register supaya dapat diambil kembali dengan cepat untuk diolah. ALU dapat melakukan operasioperasi tertentu, meliputi penjumlahan, perkalian, pengurangan, pengujian kondisi terhadap data dalam register, hingga mengirimkan hasil pemrosesannya kembali ke memori fisik, media penyimpan, atau register apabila akan mengolah hasil pemrosesan lagi. Selama proses ini terjadi, sebuah unit dalam CPU yang disebut dengan penghitung program akan memantau instruksi yang sukses dijalankan supaya instruksi tersebut dapat dieksekusi dengan urutan yang benar dan sesuai.

#### 2.2 Mikroprosesor 8085

Mikroprosesor 8085 merupakan mikroprosesor 8bit produksi INTEL, diluncurkan sekitar tahun 1970. Pada zamannya sempat dijadikan sebagai mikroprosesor standar untuk sistem operasi. Arsitektur mikroprosesor INTEL 8085 diperlihatkan dalam Gambar 2.3.

Gambar 2.3 Arsitektur Mikroprosesor 8085

Mikroprosesor 8085 ini dikemas dalam bentuk DIP (Dual Inline Package) dengan jumlah penyemat sebanyak 40 buah. Dibandingkan pendahulunya 8080, mikroprosesor 8085 hanya membutuhkan sumber tegangan.

Mikroprosesor 8085 memiliki jumlah bus alamat sebanyak 16bit dengan demikian dapat mengakses memori secara langsung sebanyak 216 alamat memori atau sebanyak 65535 alamat, sering disebut sebagai 64K x 8Bit atau 64KByte memori secara langsung. Jumlah bus data adalah 8 bit, dengan demikian dapat menghubungi peripheral dengan lebar data (Data Path Width) 8bit.

Mikroprosesor ini tidak memiliki bus alamat 16bit secara terpisah, tetapi bus alamat byte terendah (low significant byte) yaitu A0..A7 dimultiplek dengan Bus Data D0..D7. Dengan demikian mikroprosesor 8085 belum siap dijadikan sebagai Unit

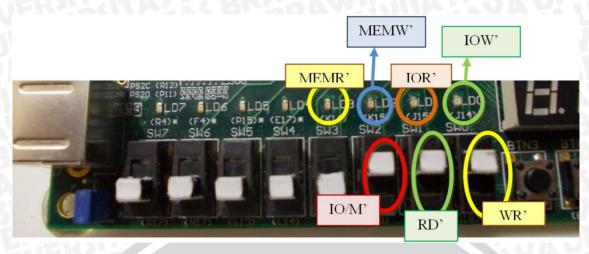

Mikroprosesor (MPU - Microprocessor Unit). Selain itu bus kontrol peripheral /MEMR, /MEMW, /IOR, dan /IOW belum terpisah sepenuhnya dan harus dibangkitkan dari sinyal kontrol /RD (penyemat 32), /WR (penyemat 31), IO/M (penyemat 34). Agar siap dijadikan sebagai MPU diperlukan beberapa komponen tambahan yaitu rangkaian bus demultiplexer (pemisahan bus D0..D7 dan A0..A7) dan rangkaian dekoder sinyal kontrol.

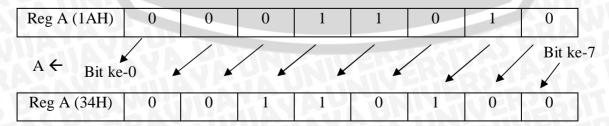

Register yang dimiliki mikroprosesor 8085 adalah sebagai berikut.

- 1) Register Akumulator (register A) yang mempunyai kapasitas 8 bit.

- 2) Register B, C, D, E, H, L. Dapat diperlakukan sebagai register 8bit atau pasangan register 8 bit menjadi 16 bit yaitu BC, DE dan HL. Register ini disebut sebagai User Register artinya register yang diperuntukkan pengguna agar bisa dilibatkan dalam pemrograman.

- 3) Register PC (Program Counter), berfungsi sebagai pointer alamat program yang akan dieksekusi.

#### 2.2.1 Siklus Prosesor

Waktu yang diperlukan 8085 untuk menangkap dan mengeksekusi satu instruksi bahasa mesin disebut siklus instruksi. Tiap-tiap instruksi memiliki kekompleksan yang berbeda-beda dengan konsekuensi semakin kompleks instruksi maka semakin panjang pula waktu untuk mengeksekusi. Metode 8085 untuk mengeksekusi instruksi di dalam mikroprosesor terorganisir sehingga waktu yang dibutuhkan untuk mengeksekusi masing-masing instruksi lebih dapat diprediksi dan lebih umum.

Masing-masing instruksi dibagi ke dalam satu hingga lima siklus mesin. Masing-masing siklus mesin pada dasarnya hasil dari yang diperlukan, oleh instruksi yang dieksekusi, untuk mengakses memori. Instruksi tersingkat dapat membutuhkan hanya satu siklus mesin., dimana instruksi tersebut diperoleh dari memori. Siklus terpanjang, yang membutuhkan lima buah siklus mesin, dapat mengakses memori sebanyak 5 kali akses, akses pertama untuk memperoleh 1 byte instruksi itu sendiri, siklus kedua dan ketiga diperlukan untuk menangkap dua byte dari suatu alamat, sedangkan siklus keempat dan kelima dibutuhkan untuk menyimpan 2 byte alamat dalam memori.

Tipe siklus mesin yang dieksekusi telah dispesifikasi berdasar status IO/M, S0, dan S1, serta jalur kontrol yaitu, /RD, /WR, dan /INTA. Keenam jalur ini dapat menetapkan tujuh tipe siklus mesin yang berbeda seperti yang dijelaskan sebagai berikut.

#### 1) Pengambilan op-code (*Op-code Fetch*)

Op-code fetch adalah siklus mesin yang pertama untuk setiap instruksi. Proses ini diinisialisasikan dengan S0 dan S1 berlogika tinggi, dengan IO/M dan /RD berlogika rendah. Proses yang terjadi adalah siklus pembacaan memori untuk memperoleh satu byte instruksi.

#### 2) Pembacaan memori (*Memory Read*)

Siklus ini adalah siklus pembacaan byte lain kecuali op-code. Proses ini diinisialisasikan dengan S0 diset 0 dan S1 diset 1, dan IO/M dan /RD berlogika rendah. Proses yang terjadi adalah siklus pembacaan memori untuk memperoleh satu byte data atau alamat.

#### 3) Penulisan Memori (*Memory Write*)

Siklus ini adalah siklus normal penulisan ke memori. Proses ini diinisialisasikan dengan S0 diset 1, S1 diset 0, dan IO/M dan /WR berlogika rendah. Proses yang terjadi adalah siklus penulisan ke memori untuk menyimpan satu byte data pada suatu alamat.

#### 4) Pembacaan Input/Output (I/O Read)

Siklus ini adalah siklus normal pembacaan suatu devais I/O. Proses ini diinisialisasikan dengan S0 diset 0, S1 diset 1, dan IO/M berlogika tinggi dan /RD berlogika rendah. Proses yang terjadi adalah siklus pembacaan ang akan membawa satu byte dari suatu devais input ke dalam mikroprosesor.

#### 5) Penulisan Input/Output (*I/O Write*)

Siklus ini adalah siklus normal penulisan ke I/O. Proses ini diinisialisasikan denagan S0 diset 1, S1 diset 0, dan IO/M dan /WR berlogika rendah. Proses yang terjadi adalah siklus penulisan yang akan mengirimkan satu byte keluar dari mikroprosesor ke suatu devais output.

#### 2.3 Memori

Memori adalah pusat kegiatan pada sebuah komputer, karena setiap proses yang akan dijalankan harus melalui memori terlebih dahulu. CPU mengambil instruksi dari memori sesuai dengan yang ada pada program counter. Tugas sistem operasi adalah mengatur peletakan banyak proses pada suatu memori.